# Screening-engineered Field-effect Photovoltaics and Synthesis, Characterization, and Applications of Carbon-based and Related Nanomaterials

by

#### William Raymond Regan

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Physics

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Alex K. Zettl, Chair Professor Michael F. Crommie Professor Ali Javey

Fall 2012

# Screening-engineered Field-effect Photovoltaics and Synthesis, Characterization, and Applications of Carbon-based and Related Nanomaterials

$\begin{array}{c} \text{Copyright 2012} \\ \text{by} \\ \end{array}$  William Raymond Regan

#### Abstract

Screening-engineered Field-effect Photovoltaics and Synthesis, Characterization, and Applications of Carbon-based and Related Nanomaterials

by

William Raymond Regan

Doctor of Philosophy in Physics

University of California, Berkeley

Professor Alex K. Zettl, Chair

Carbon nanomaterials, and especially graphene (a 2D carbon allotrope), possess unique electronic, optical, and mechanical properties and allow access to both new physical phenomena and reinventions of familiar technologies. In the first part of this thesis (chapter 2), the low carrier density and high conductivity of graphene are used to repurpose the electric field effect (used for many decades in transistors) into a universally-applicable doping method for electrically-contacted semiconductors. This method, referred to as "screening-engineered field-effect photovoltaics" as the electric field doping is enabled by a carefully-designed poorly-screening electrode (e.g. graphene), is shown to open up many new low-cost and abundant semiconductors for use in high efficiency solar cells. We extend this method beyond ultrathin materials such as graphene and show that 1D nanowire electrodes made of any material also allow penetration of applied electric fields. The next part of this thesis (chapter 3) focuses on the fundamental properties of graphene – its structure, synthesis, characterization, and manipulation – and on using graphene as a building block for other nanostructures: grafold, graphene sandwiches and veils, and graphritos. In chapter 4, various graphene electronics are constructed and tested. Graphene field-effect transistors (FETs) and p-n junctions are fabricated to study the influence of the substrate on graphene carrier mobility and doping. Graphene nanoribbons and grafold FETs are made to investigate the effects of additional confinement on electronic transport. Chapter 5 summarizes synthesis methods and additional experiments with other nanomaterials, including dichalcogenides and chalcogenides (magnesium diboride, gallium selenide, and tin sulfide), carbon nanomaterials (carbon nanotubes and graphene), and copper oxide. Additional measurement and fabrication methods are discussed in appendix A.

To Vicki

# Contents

| Li       | st of | Figures                                                 | iv  |

|----------|-------|---------------------------------------------------------|-----|

| Li       | st of | Tables                                                  | vii |

| 1        | Intr  | roduction                                               | 1   |

| <b>2</b> | Scre  | eening-engineered field-effect photovoltaics            | 3   |

|          | 2.1   | Background, promise, and challenges                     | 3   |

|          |       | 2.1.1 Structure of an inorganic solar cell              | 3   |

|          |       | 2.1.2 Challenges in p-n junction formation              | 3   |

|          |       | 2.1.3 Gating with an electric field                     | 4   |

|          | 2.2   | Screening-engineering for effective gating              | 5   |

|          | 2.3   | SFPV based on silicon Schottky junctions                | 7   |

|          |       | 2.3.1 Ultrathin contact (graphene) SFPV                 | 8   |

|          |       | 2.3.2 Nanofinger SFPV: ohmic and Schottky contacts      | 13  |

|          | 2.4   | Self-contained gating for practical SFPV cells          | 20  |

|          | 2.5   | Criteria for promising SFPV semiconductors              | 22  |

|          |       | 2.5.1 Cuprous oxide                                     | 24  |

|          |       | 2.5.2 Other candidate materials in progress             | 25  |

|          | 2.6   | Conclusions and future work                             | 28  |

| 3        | Gra   | phene and carbon nanomaterials                          | 29  |

|          | 3.1   | Background                                              | 29  |

|          | 3.2   | Graphene growth by CVD                                  | 30  |

|          | 3.3   | Manipulation of CVD graphene                            | 33  |

|          |       | 3.3.1 Polymer-supported graphene transfer               | 33  |

|          |       | 3.3.2 Direct, polymer-free transfer of CVD graphene     | 35  |

|          |       | 3.3.3 Transfer-free synthesis of suspended CVD graphene | 36  |

|          | 3.4   | Characterization of CVD graphene                        | 39  |

|          |       | 3.4.1 Optical microscopy of graphene                    | 39  |

|          |       | 3.4.2 Raman spectroscopy of graphene                    | 39  |

|          |       | 3.4.3 TEM studies of graphene                           | 42  |

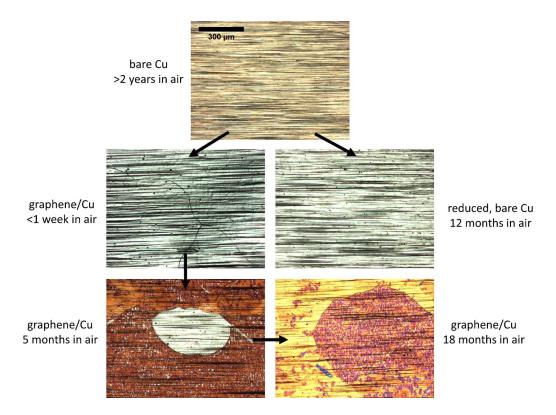

|              |       | 3.4.4 Graphene's mixed success as an oxidation barrier              | 45  |

|--------------|-------|---------------------------------------------------------------------|-----|

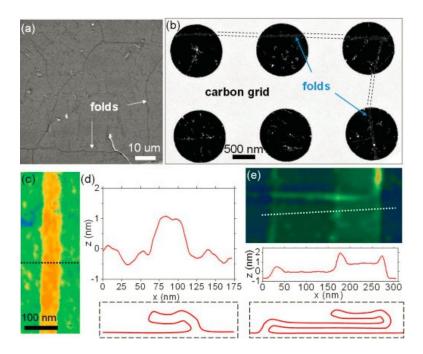

|              | 3.5   | Novel graphene superstructures                                      | 50  |

|              |       | 3.5.1 Grafold                                                       | 50  |

|              |       | 3.5.2 Graphene sandwiches and veils                                 | 50  |

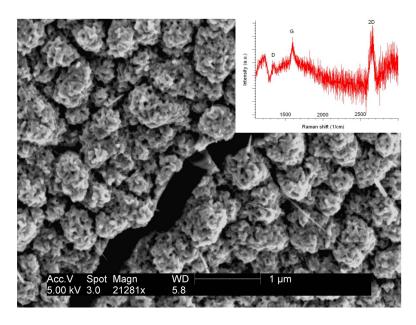

|              |       | 3.5.3 Graphritos                                                    | 52  |

| 4            | Gra   | phene electronics                                                   | 55  |

| _            | 4.1   | Basic properties                                                    | 55  |

|              | 4.2   | High electronic mobility graphene FETs                              | 56  |

|              | 1.2   | 4.2.1 Additional comparisons of hBN and SiO <sub>2</sub> substrates | 60  |

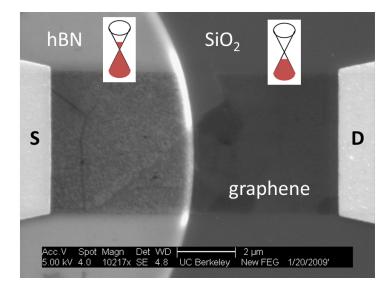

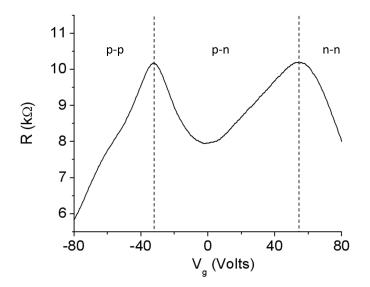

|              | 4.3   | Graphene p-n junction                                               | 62  |

|              | 4.4   | Graphene nanoribbons via BNNT etch masks                            | 65  |

|              | 4.5   | Grafold transport                                                   | 68  |

|              |       | 4.5.1 Grafold to nanoribbons via fluorination                       | 71  |

| 5            | Syn   | thesis methods and other research                                   | 72  |

|              | 5.1   | Magnesium diboride                                                  | 72  |

|              | 5.2   | Carbon nanotubes                                                    | 72  |

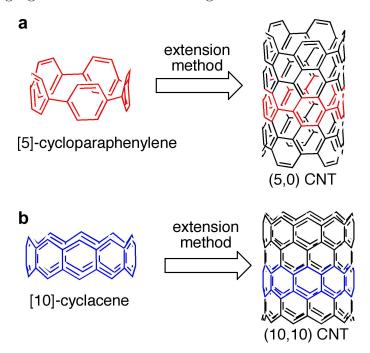

|              |       | 5.2.1 Controlled chirality nanotubes                                | 74  |

|              |       | 5.2.2 Patterned carbon nanotubes via Co abrasion                    | 78  |

|              | 5.3   | Alternate methods of graphene synthesis                             | 78  |

|              |       | 5.3.1 Graphene exfoliation                                          | 78  |

|              |       | 5.3.2 CVD growth of graphene on Cu and hBN thin films               | 79  |

|              |       | 5.3.3 One-step graphene devices on thin copper films                | 82  |

|              | 5.4   | Chalcogenide growth via Bridgman technique                          | 82  |

|              |       | 5.4.1 Gallium selenide (GaSe) growth                                | 84  |

|              |       | 5.4.2 Tin sulfide (SnS and SnS <sub>2</sub> ) growth                | 87  |

|              | 5.5   | Cuprous oxide growth                                                | 89  |

|              |       | 5.5.1 High temperature growth on thick Cu foils                     | 89  |

|              |       | 5.5.2 Thin film cuprous oxide growth                                | 92  |

| Bi           | bliog | graphy                                                              | 94  |

| $\mathbf{A}$ | Fab   | rication and measurement techniques                                 | 105 |

|              | A.1   | Photovoltaic measurements                                           | 105 |

|              |       | A.1.1 In-tipped pin probes for fragile contacts                     | 105 |

|              | A.2   | Lithography and evaporation tips and tricks                         | 108 |

|              |       | A.2.1 Sputtered or thick contacts                                   | 109 |

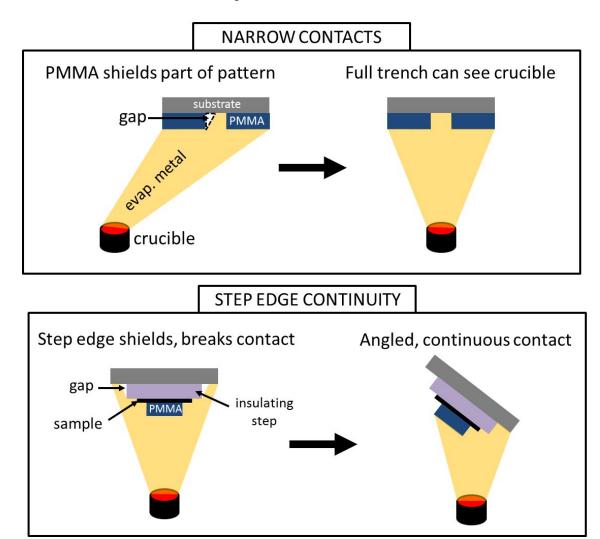

|              |       | A.2.2 Evaporation pitfalls: narrow contacts and step edges          | 109 |

|              | A.3   | Cuprous oxide: surface treatments and SFPV devices                  | 110 |

|              | A.4   | Piranha etching                                                     | 113 |

# List of Figures

| 2.1  | An inorganic solar cell and corresponding band diagram                        | 4  |

|------|-------------------------------------------------------------------------------|----|

| 2.2  | Screening while gating a Schottky barrier solar cell                          | 6  |

| 2.3  | SFPV cell using a graphene top contact                                        | 6  |

| 2.4  | SFPV cell using a "nanofinger" top contact                                    | 7  |

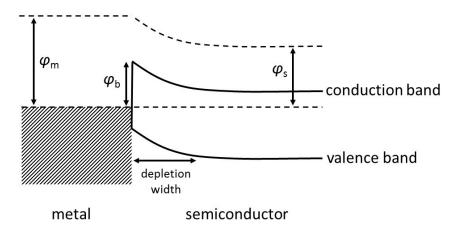

| 2.5  | Schottky junction band diagram                                                | 8  |

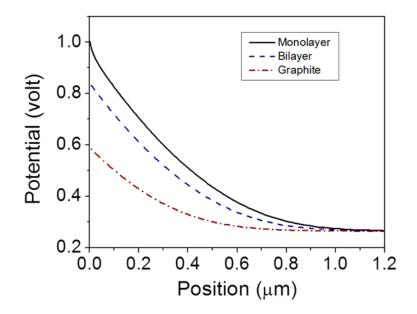

| 2.6  | Potential in Si with saturated gate for 1-, 2-, and many-layer graphene       | 10 |

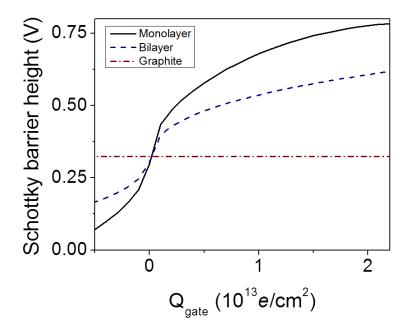

| 2.7  | Schottky barrier height versus $Q_{gate}$ for 1-, 2-, and many-layer graphene | 10 |

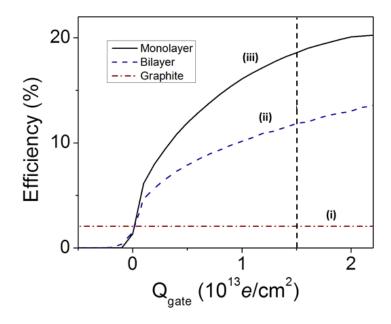

| 2.8  | Efficiency versus Versus $Q_{gate}$ for 1-, 2-, and many-layer graphene       | 11 |

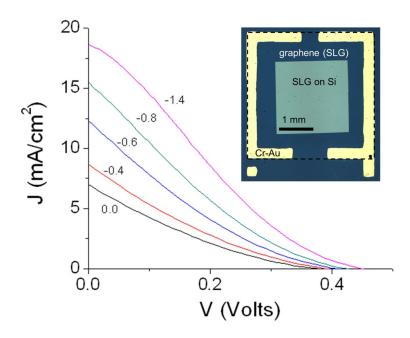

| 2.9  | I-V $_g$ curves versus V $_g$ for monolayer graphene SFPV cell                | 12 |

| 2.10 | Bilayer graphene SFPV cell performance versus gate voltage                    | 12 |

| 2.11 | Simulated potential plots for ohmic and Schottky nanofinger SFPV .            | 14 |

| 2.12 | Current-voltage curves for ohmic and Schottky SFPV devices                    | 15 |

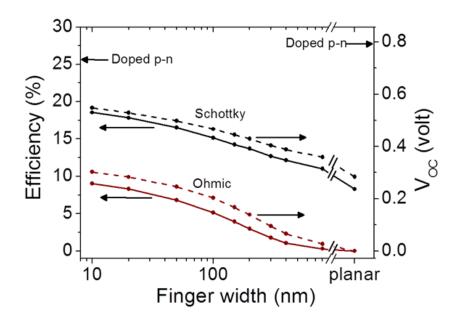

| 2.13 | Maximum efficiency and $V_{OC}$ for ohmic and Schottky nanofinger SFPV        | 16 |

| 2.14 | Effect of finger spacing on SFPV performance (fixed finger width)             | 16 |

| 2.15 | Optical micrograph of (ohmic) Al nanofinger silicon SFPV cell                 | 17 |

| 2.16 | Current-voltage curves for ohmic nanowire SFPV                                | 18 |

| 2.17 | Current-voltage curves for Schottky nanowire SFPV: positive gating .          | 19 |

| 2.18 | Current-voltage curves for Schottky nanowire SFPV: negative gating            | 19 |

| 2.19 | Self-gating SFPV performance versus finger width                              | 21 |

| 2.20 | Experimental demonstration of self-gating feedback loop                       | 21 |

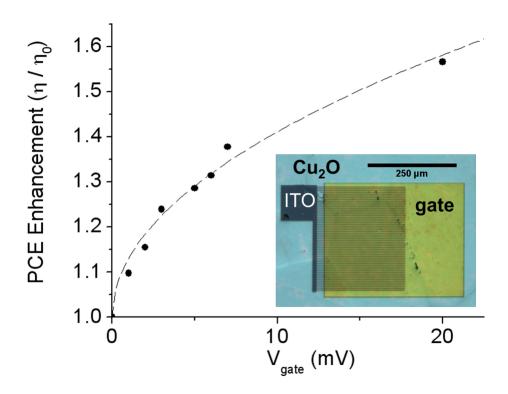

| 2.21 | Efficiency enhancement for Cu <sub>2</sub> O SFPV cells                       | 25 |

| 2.22 | SnS crystal structure                                                         | 26 |

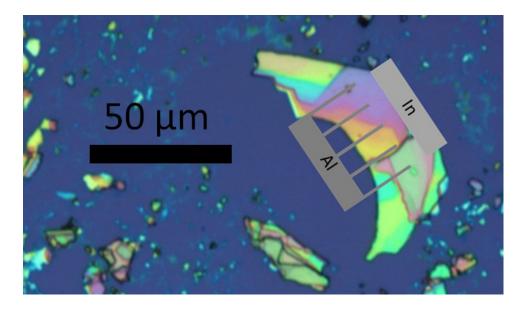

| 2.23 | Exfoliated tin sulfide single crystals on $SiO_2$                             | 27 |

| 3.1  | Graphene structure                                                            | 29 |

| 3.2  | Band structure of graphene                                                    | 30 |

| 3.3  | Zettl group carbon CVD system                                                 | 31 |

| 3.4  | Two-stage CVD graphene recipe                                                 | 32 |

| 3.5  | CVD system for graphene and hBN growth                                        | 33 |

| 3.6  | Improved graphene transfer with PMMA reflowing                                | 35 |

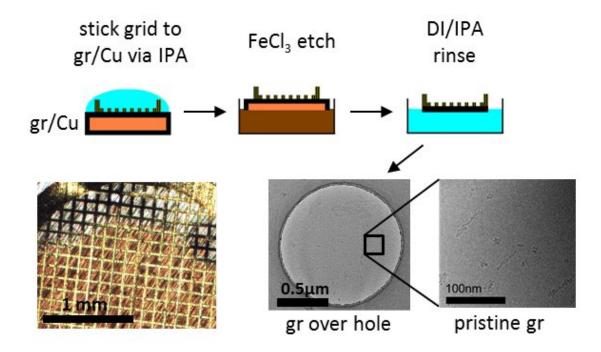

| 3.7  | Direct graphene transfer to TEM grids                                         | 36 |

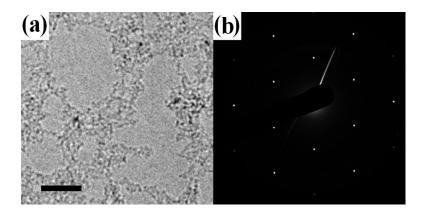

| 38   | TFM imaging and diffraction of suspended graphone                             | 37 |

| 3 | 9 Transfer-free graphene/Cu TEM grids                                    | 38 |

|---|--------------------------------------------------------------------------|----|

| 3 | 10 Graphene/Cu TEM grids                                                 | 38 |

|   |                                                                          | 39 |

| 3 | 12 Raman modes of monolayer graphene                                     | 40 |

| 3 | 13 Raman spectra for $SiO_2$ -supported and suspended graphene           | 41 |

| 3 | 14 Raman modes of rotated bilayer graphene                               | 42 |

| 3 | 15 TEM mapping of CVD graphene grains                                    | 43 |

|   | V V                                                                      | 44 |

|   | 0 1                                                                      | 45 |

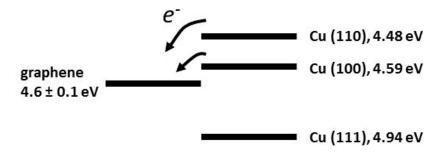

|   | 0 1                                                                      | 46 |

|   | •                                                                        | 47 |

|   |                                                                          | 48 |

|   | 0 1                                                                      | 49 |

|   | 1 /                                                                      | 49 |

|   | 1                                                                        | 51 |

| 3 |                                                                          | 52 |

|   | 1                                                                        | 53 |

|   | ○ I                                                                      | 54 |

| 3 | 27 SEM micrographs of PMMA-filled graphritos                             | 54 |

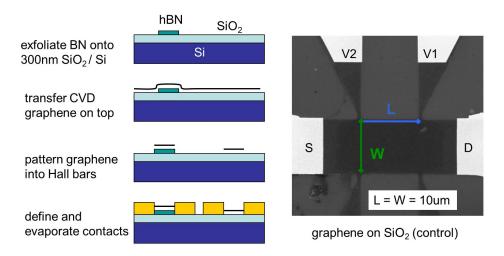

| 4 | 1 Fabrication of graphene/hBN FETs                                       | 57 |

| 4 |                                                                          | 58 |

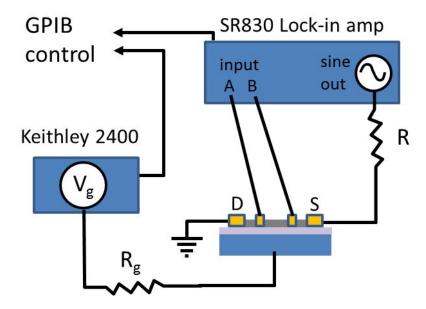

| 4 | 3 Measurement setup for gated graphene FETs                              | 58 |

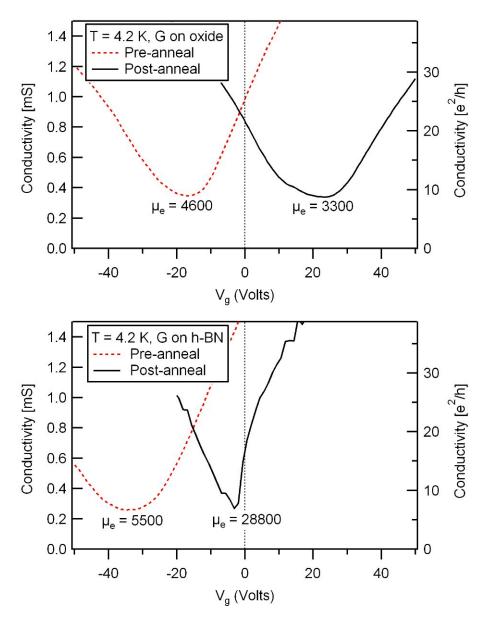

| 4 | 4 $\sigma$ versus $V_g$ for graphene FETs                                | 59 |

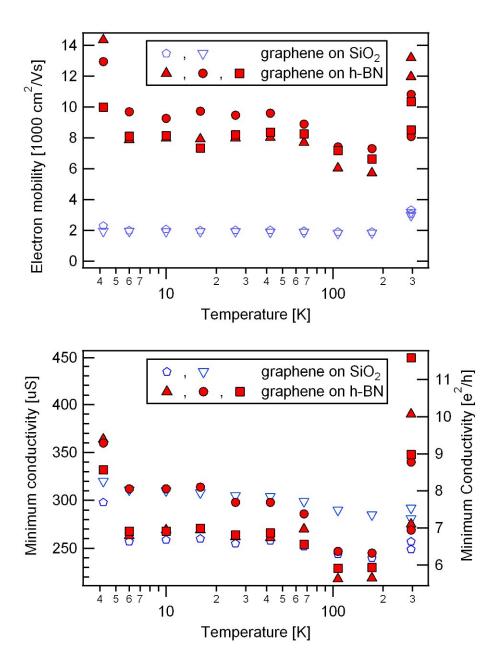

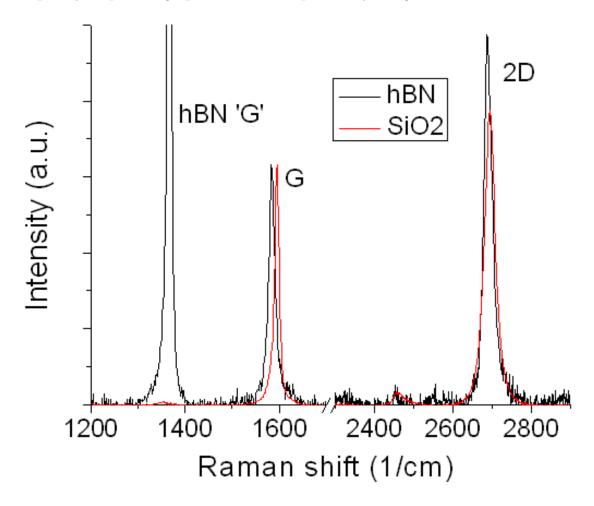

| 4 | 5 $\mu$ and $\sigma_{min}$ for graphene FETs on hBN and SiO <sub>2</sub> | 61 |

| 4 | 6 Raman spectra of hBN- and SiO <sub>2</sub> -supported graphene         | 62 |

| 4 | 7 Substrate-induced (hBN and $SiO_2$ ) graphene p-n junction             | 64 |

| 4 | $g$ $\cup$ $1$ $1$ $y$                                                   | 64 |

| 4 |                                                                          | 65 |

|   | 1                                                                        | 66 |

|   | 0 1                                                                      | 67 |

|   | 5                                                                        | 67 |

|   | 1 1                                                                      | 69 |

|   | 0 1 1                                                                    | 69 |

|   | <i>y</i> 1                                                               | 70 |

| 4 | 16 R-V <sub>g</sub> for perpendicular grafold FET                        | 71 |

| 5 | 1 01 02 0 0                                                              | 73 |

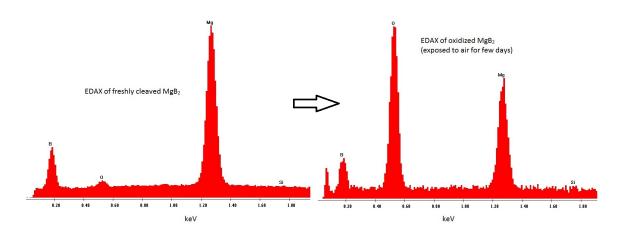

|   | 2 EDAX of freshly cleaved and oxidized $MgB_2$                           | 73 |

|   |                                                                          | 74 |

|   |                                                                          | 75 |

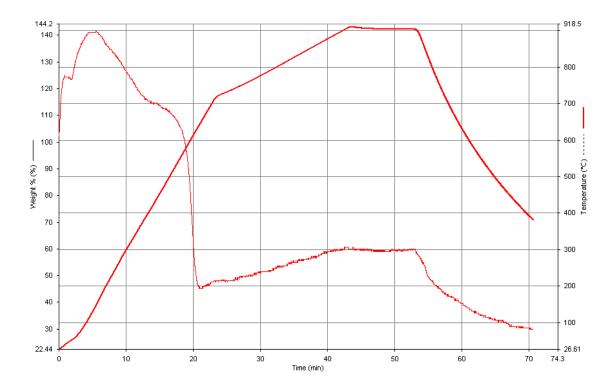

| 5 | 5 Thermogravimetric analysis of 12-cycloparaphenylene                    | 76 |

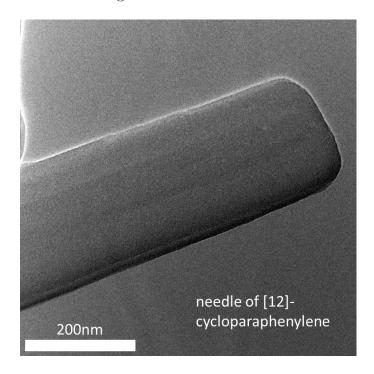

| 5.6  | TEM image of a 12-cycloparaphenylene needle                                    | 77 |

|------|--------------------------------------------------------------------------------|----|

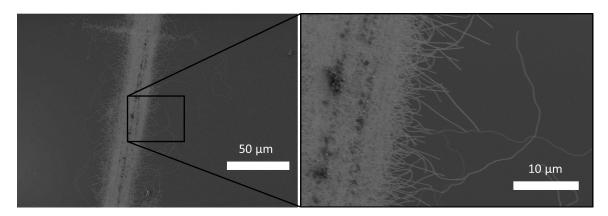

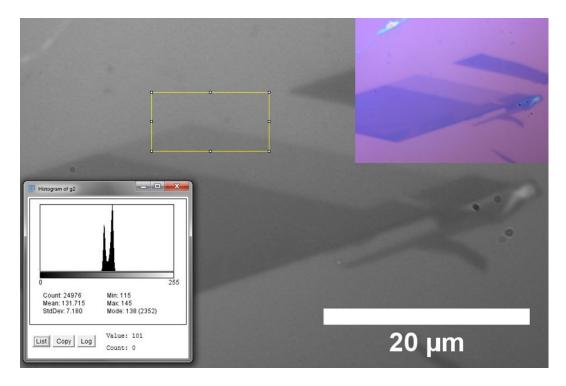

| 5.7  | SEM of CVD-grown SWCNT with abraded Co catalyst                                | 78 |

| 5.8  | Thin exfoliated graphene on 285 nm $SiO_2$                                     | 30 |

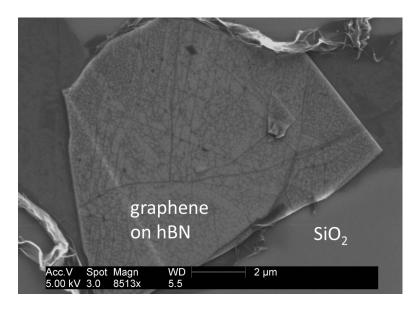

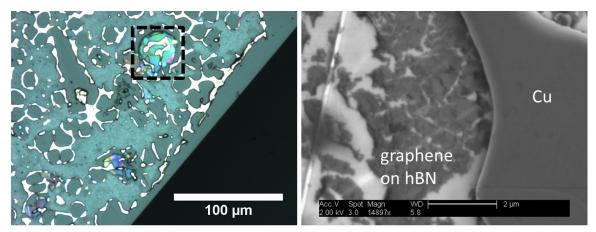

| 5.9  | Graphene on hBN enabled via Cu dewetting                                       | 31 |

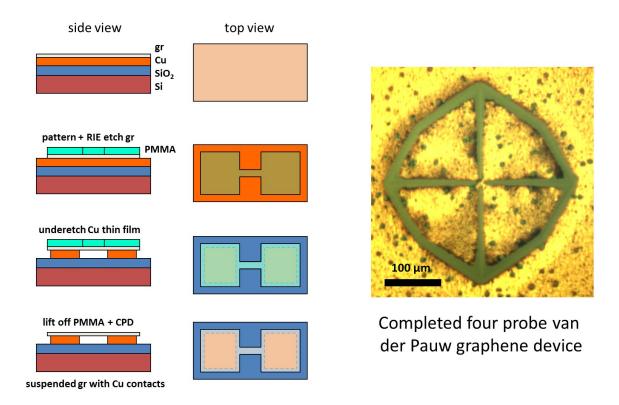

| 5.10 | Single lithography step CVD graphene devices                                   | 33 |

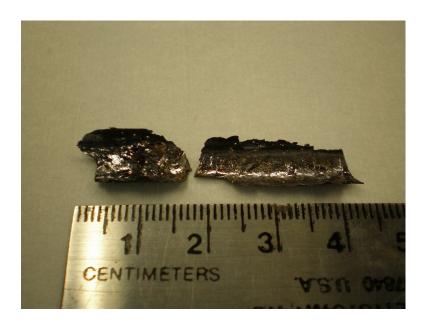

| 5.11 | Gallium selenide synthesis recipe                                              | 34 |

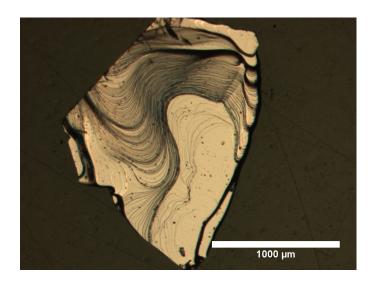

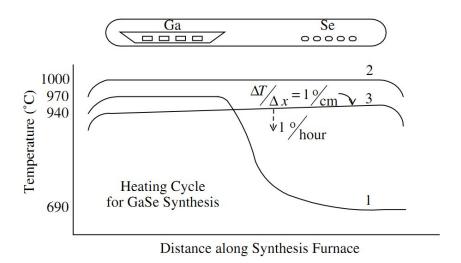

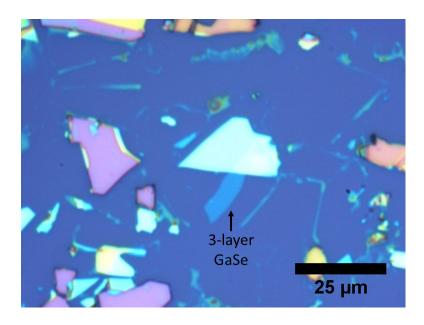

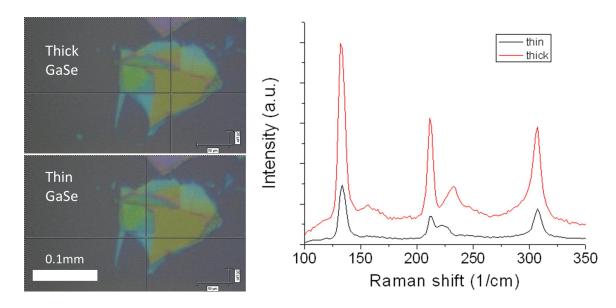

| 5.12 | Optical micrograph of GaSe boule                                               | 35 |

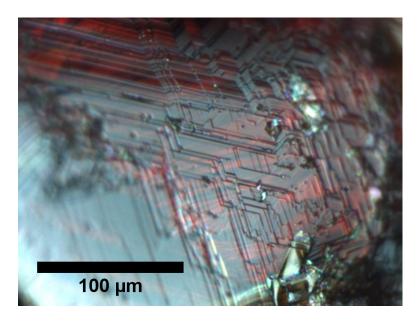

| 5.13 | Few-layer exfoliated GaSe on $SiO_2/Si$                                        | 36 |

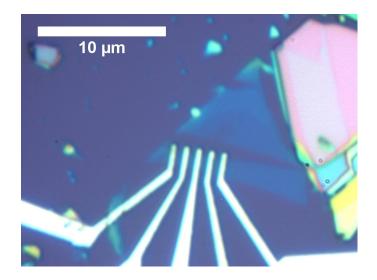

| 5.14 | Raman spectra of exfoliated GaSe                                               | 36 |

| 5.15 | Bilayer GaSe on $SiO_2/Si$ with In contacts                                    | 37 |

| 5.16 | Boule of tin sulfide grown with the Bridgman technique                         | 38 |

| 5.17 | Tape exfoliated tin sulfide on $300 \text{nm SiO}_2$ on Si wafer 8             | 38 |

| 5.18 | Raman of exfoliated SnS (shown to be $SnS_2$ )                                 | 39 |

| 5.19 | Pressure-temperature phase diagram of copper oxides                            | 90 |

| 5.20 | Recipe for high temperature Cu <sub>2</sub> O foil growth                      | )1 |

| 5.21 | - 0 0 1 7 1                                                                    | )1 |

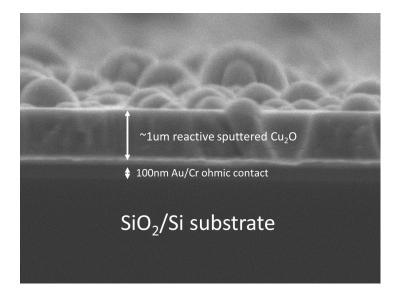

| 5.22 | Reactive oxygen sputtered Cu <sub>2</sub> O on Au/SiO <sub>2</sub> /Si         | 92 |

| 5.23 | Absorption versus wavelength for reactive sputtered CuO and $\mathrm{Cu_2O}$ . | 93 |

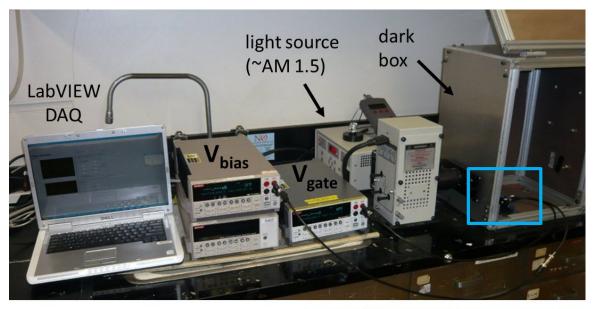

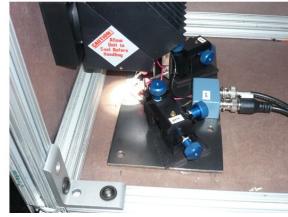

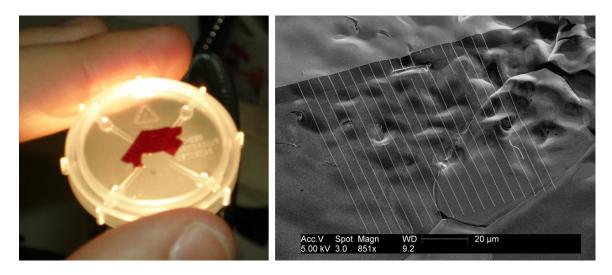

| A.1  | Zettl Group photovoltaic measurement system                                    | )6 |

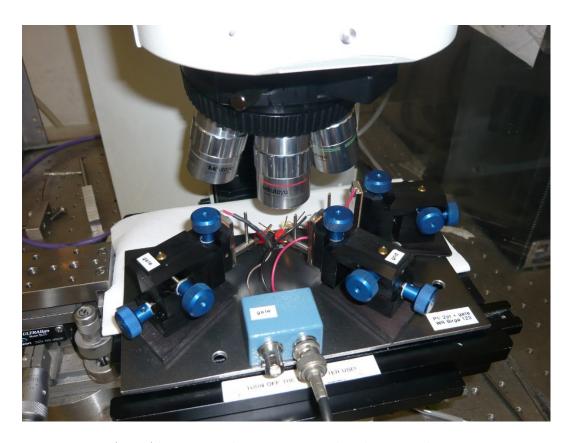

| A.2  | Aligning probe contacts under the optical microscope                           | )7 |

| A.3  | Applying light to probe station from above or below                            | )7 |

| A.4  | SEM image of developed MMA PMMA bilayer                                        | )9 |

| A.5  | Evaporation with narrow contacts or step edges                                 | LO |

| A.6  | Breaks in contacts on unpolished $Cu_2O$                                       | 1  |

| A.7  | SFPV devices made with polished $Cu_2O$                                        | 12 |

| A.8  | SFPV device made with thin film, low temperature Cu <sub>2</sub> O 11          | 12 |

# List of Tables

| 2.1 | Abundance and efficiency limits of non-silicon semiconductors      | Ę  |

|-----|--------------------------------------------------------------------|----|

| 2.2 | Areal charge density for inversion as a function of Si bulk doping | 22 |

| 2.3 | A few candidate materials for SFPV cells                           | 23 |

| 2.4 | Cu/Cu <sub>2</sub> O planar and SFPV simulations                   | 24 |

#### Acknowledgments

I wish to thank Professor Alex Zettl, who has been an excellent advisor. He has given me great ideas and advice as well as the freedom and encouragement to explore my own ideas. Additionally, the facilities (and of course the colleagues) in the Zettl lab are second to none; anything is possible in the incredible research environment he has built.

I wish to thank the many other professors who have given generously of their time and expertise. I am grateful to Professor Michael Crommie, who has served so many roles – a great advisor during research rotations, a frequent collaborator in recent years, and a helpful member of both my qualifying exam (as chair) and thesis committees. I thank Professor Ramamoorthy Ramesh for the advice which helped bring me to Berkeley and for his mentorship during my research rotations. Professor Feng Wang has been an excellent and insightful collaborator over the years, and I am also thankful for his service on my qualifying exam committee. It was also a great privilege to collaborate with Professors Marvin Cohen, Alessandra Lanzara, and Carolyn Bertozzi. I am grateful to Professor Mark Asta for serving on my qualifying exam committee and to Professor Ali Javey for kindly serving on my thesis committee. Finally, it has been great working with Dr. Willi Mickelson, a master of the quick, intuitive experiment (thought or tangible).

I am grateful to my colleagues for their friendship, encouragement, and insight. Dr. Çağlar Girit and Dr. Benji Alemán were excellent role models and mentors; their advice and training was formative in my graduate studies. Their patience with a new, fumbling grad student (especially considering how busy they were as senior grad students and new fathers) speaks highly of their character. Nearly all projects in this thesis were some form of collaboration with Will Gannett, a great experimentalist, friend, and trivia buff. The photovoltaics work was done with Steven Byrnes (of Professor Feng Wang's group), another good friend and smart fellow. It has been a pleasure working with Kwanpyo Kim and being a part of his many successful projects. I would also like to thank the many other Zettl group members who have helped and have made going to work a pleasure: Dr. Matthias Loster, Dr. David Okawa, Dr. Nasim Alem, Dr. Jianhao Chen, Maria Schriver, Kris Erickson, Allen Sussman, and many others. I am also very grateful to Gee Gee Lang and Anne Takizawa for cutting all sorts of red tape, making things happen, and being nice people in times of stress.

I am grateful to the Achievement Rewards for College Scientists (ARCS) Foundation and the National Science Foundation for their significant financial support.

Finally, I owe a tremendous debt to my family – especially Dr. Barbara Hamilton, Raymond Regan, and Ernest F. Hamilton, Jr. – for their hard work, encouragement, and understanding.

This thesis is dedicated to Vicki Hsieh for her constant support and for believing in me.

# Chapter 1

# Introduction

This is an exciting time to study nanomaterials. With the explosion of computing power in the past few decades and development of several new experimental techniques to fabricate 1D and 2D materials, there has perhaps never been more low-hanging fruit. In just one example, the many possible chiralities of single walled carbon nanotubes that can be sythesized has been equated to suddenly opening up a new periodic table.

In this thesis, I discuss my work on 1D and 2D nanomaterials, with special emphasis on graphene, a single-atom-thick sheet of sp<sup>2</sup>-bonded carbon. I begin by focusing on an ongoing photovoltaics project that touches on many aspects of my research, materials synthesis (both quasi-1D and 2D materials) and fabrication/measurement of electronic devices. In later chapters, I expand upon these concepts in greater depth, focusing especially on the synthesis, manipulation, and application of graphene. I then describe the synthesis and application of other nanomaterials and close with a section on tips and tricks developed for fabrication and testing.

In chapter 2, I explain how graphene's optical and electronic properties inspired a new type of solar cell design called "screening-engineered field-effect photovoltaics" (SFPV). The SFPV concept uses a partially screening electrode to allow an applied electric field to tune the carrier density and type of a semiconductor, accomplishing the same effect as chemical doping in a manner that is compatible with any semiconductor. SFPV designs for graphene (2D) and nanowire (1D) partially-screening electrodes will be discussed, along with ways to sustain the applied electric field internally.

Chapter 3 covers graphene theory, synthesis (by chemical vapor deposition, or CVD), characterization, and manipulation. I discuss optimization of synthesis methods and an ultraclean graphene transfer process, which together have paved the way for in-depth fundamental studies of CVD graphene properties. This chapter also includes discussion on our discovery and studies of several graphene nanostructures: grafold, graphene sandwiches/veils, and "graphritos."

In chapter 4, I discuss electronic devices made with CVD graphene: field-effect

transistors (FETs), p-n junctions, nanoribbons, and grafold FETs. Our studies of graphene FETs reveal that the graphene substrate is a dominant source of scattering for CVD graphene, and the use of hBN as opposed to SiO<sub>2</sub> is sufficient to attain very high mobilities (enough to explore much of the rich physics of 2DEGs) for present-day CVD graphene. The graphene p-n junctions also make us of substrate effects, particularly the difference in doping seen on hBN and SiO<sub>2</sub> subtrates. Likewise, our studies of nanoribbons make use of the excellent properties of boron nitride (in this case, boron nitride nanotubes or BNNT).

Chapter 5 summarizes other nanomaterial synthesis methods and related projects completed and in progress. Materials include  $MgB_2$ , carbon nanotubes (CNT), graphene (exfoliation, additional CVD methods using thin catalyst films), chalcogenides (GaSe and SnS), and copper oxide (Cu<sub>2</sub>O).

In the appendix (chapter A), I record several tips and tricks of fabrication and device measurement which I hope will save future group members time and frustration.

# Chapter 2

# Screening-engineered field-effect photovoltaics

## 2.1 Background, promise, and challenges

Global electricity demand is presently around 17,000 TWh per year. Incident sunlight bombards the earth with over 8,000 times this much power. Not surprisingly, photovoltaic energy conversion is expected to play a major role in fulfilling our future energy needs. However, present technologies cannot harvest this power in a sufficiently cost-effective way, due to a combination of raw material and processing costs [79, 103].

#### 2.1.1 Structure of an inorganic solar cell

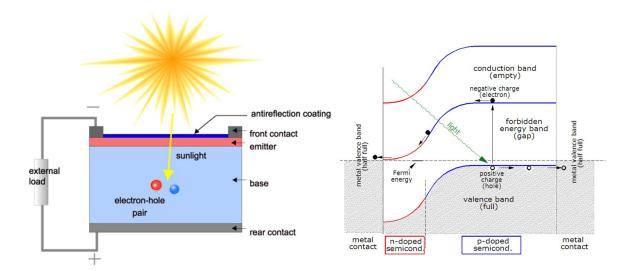

A schematic of a typical inorganic solar cell and a corresponding band diagram are shown in figure 2.1. The base is a singly-doped semiconductor, and the emitter is a thinner, oppositely-doped semiconductor. Light is absorbed (and excitons are created) primarily in the thicker base region. The excitons are weakly bound (Mott-Wannier excitons) and dissociate easily into holes and electrons at room temperature. These freed carriers then diffuse and drift to regions where they are majority carriers, pushed by the internal electric field set up by the p-n junction. Once the photoexcited carriers become majority carriers, recombination is much less likely, and they can be extracted by the metal contacts.

## 2.1.2 Challenges in p-n junction formation

Commercial-scale production of inorganic solar cells<sup>1</sup> has so far relied on a limited subset of semiconductors which can be divided into two distinct classes, (1) materials

<sup>&</sup>lt;sup>1</sup>Dye-sensitized and organic photovoltaics, so-called excitonic solar cells due to the strong exciton binding (Frenkel excitons) relative to the weak exciton binding (Mott-Wannier excitons) in most inorganic p-n junction cells, will not be discussed in this work.

Figure 2.1: A typical inorganic solar cell (left, source: pvcdrom.pveducation.org) and corresponding band diagram (right, source: wikipedia.org). Light is absorbed and creates excitons in the thick base material, which is p-doped in this example. Excitons dissociate into electrons and holes easily; these charge carriers feel the electric field created by the p-n junction and drift into regions where they are majority carriers, where they are then extracted at the metal contacts.

that can be easily doped (Si, GaAs, InP) and (2) materials that make reasonable p-n heterojunctions, such as p-type CdTe or CIGS heterojunctions with n-type CdS.

However, there are many other semiconductors with bandgaps that sit near the peak of the Shockley-Queisser efficiency limit curve [87]. Many of these high-efficiency potential materials are also extremely abundant and affordable (metal oxides, phosphides, sulfides, etc), as shown in table 2.1, but most cannot be doped or form poor heterojunctions [100].

## 2.1.3 Gating with an electric field

In the absence of ways to dope or form good heterojunctions with the earth-abundant semiconductors, it may seem that these materials can never be used for low-cost, high-efficiency photovoltaics. However, there are other methods besides doping to tune or even invert the carrier concentration in semiconductors, namely applying an electric field by gating as is commonly done in metal-oxide-semiconductor field-effect transistors (MOSFETs). One might imagine that this gating strategy could entirely displace the need for doping, allowing local inversion of a p-type semiconductor into a n-type semiconductor. Indeed, the use of effective gating in photovoltaics is a several decades old strategy, begining with metal-insulator-semiconductor (MIS) solar cells, in which a thin insulating layer is used to block recombination current. MIS cells

| Material                    | Annual production potential (TWh) | Efficiency limit (%) |

|-----------------------------|-----------------------------------|----------------------|

| CIGS                        | 5,000                             | 33                   |

| CdTe                        | 60                                | 32                   |

| $\mathrm{FeS}_2$            | 500,000,000                       | 30                   |

| CuO                         | 10,000,000                        | 26                   |

| $Cu_2S$                     | 10,000,000                        | 33                   |

| $Zn_3P_2$                   | 9,000,000                         | 31                   |

| $\mathrm{Bi}_2\mathrm{S}_3$ | 4,000                             | 33                   |

Table 2.1: Abundance and efficiency limits of non-silicon semiconductors. Current heterojunction fabrication techniques limit industry to using only CIGS and CdTe. Many of the more abundant materials (FeS<sub>2</sub> especially) cannot be doped and form poor heterojunctions [100].

employ fixed, uncompensated charges within a dielectric coating (often  $Cs^+$  in  $Si_3N_4$ ) to increase the semiconductor band bending at the MIS interface. These cells have achieved high efficiencies [40, 106, 107] but have notoriously short operating lifetimes due to the instability of surface states under illumination [37]. Implementation of direct gate "doping," where a metal-insulator gate is used to invert a region of semi-conductor [27, 32, 106, 107] is limited by screening of the gate near the top contact, as illustrated in figure 2.2. These gating methods must rely on strategies such as doping under the top contacts [27, 32] or the formation of a large Schottky barrier at the top contacts [40, 106, 107], both of which are incompatible with the earth-abundant semiconductors discussed above. Some success has been achieved with low density-of-states Schottky contacts [66, 98, 99], but such approaches will not necessarily work for any semiconductor.

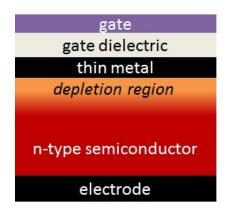

## 2.2 Screening-engineering for effective gating

The core challenge in achieving effective gate-induced doping (without relying on chemical doping or large intrinsic Schottky barriers) is that the electrode beneath the gate must simultaneously conduct well (to be an effective and low series resistance contact) but also have few enough charge carriers that the charge induced by the gate field is shared between the contact and the underlying semiconductor. Graphene, a single-atom thick sheet of hexagonally-bonded carbon (as will be discussed in detail in the following chapters), satisfies these two seemingly contradictory requirements. Graphene has very few charge carriers near its neutrally doped state, but has a remarkably low sheet resistance of  $500\Omega/\Box-1k\Omega/\Box$ ; in addition, monolayer graphene is fairly transmittive, only absorbing  $\pi\alpha \sim 2.3\%$  of visible light [22, 71]. Thus, when gating a monolayer graphene contact on a semiconductor (as seen in figure 2.3), the induced charge can be shared between the graphene and semiconductor. The resulting

Gate field is screened by even very thin metal

Figure 2.2: This schematic illustrates the challenge of using an applied electric field to tune a Schottky barrier solar cell. For any practical top electrode, the applied gate field will be screened, preventing effective carrier modulation in the semiconductor.

cell is hereafter referred to as a screening-engineered field-effect photovoltaic (SFPV) cell. Much of the remaining work in this chapter was done in collaboration with Steven Byrnes of Professor Feng Wang's group at UC Berkeley, along with assistance from Will Gannett, Onur Ergen, and Dr. Oscar Vazquez-Mena of the Zettl group. Steven performed all theoretical calculations, and additional information on these calculations can be found in his PhD thesis, currently in preparation. Several of the following sections also contain information found in our recent *Nano Letters* article [82].

Graphene's poor screening allows tuning of graphene-nSi Schottky junction.

Figure 2.3: Screening-engineered field-effect photovoltaic (SFPV) cell using a graphene top contact. Graphene allows simultaneous contact to and carrier modulation (with an applied electric field) of the underlying semiconductor.

This first instance of a SFPV cell requires an ultrathin contact. As more graphene layers are added to decrease sheet resistance, the tunability of the junction is diminished; when the monolayer graphene layer in contact with the semiconductor no longer shares any of the induced charge, the semiconductor can no longer be influenced by

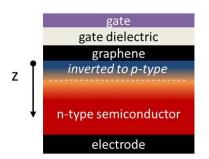

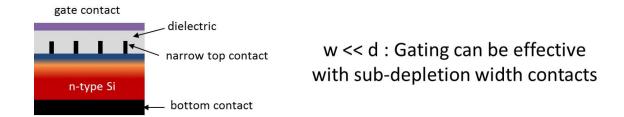

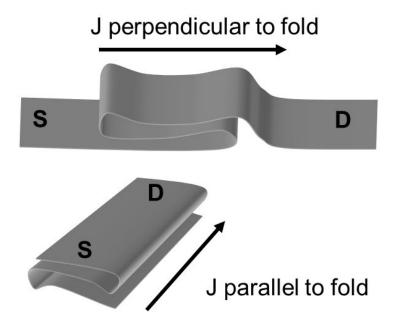

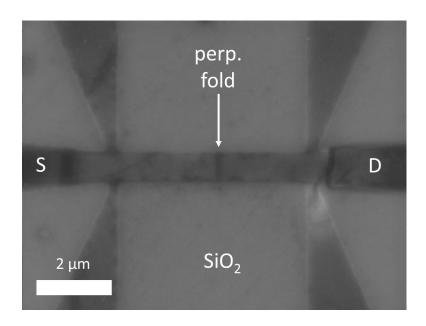

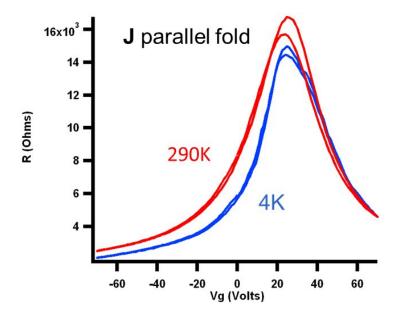

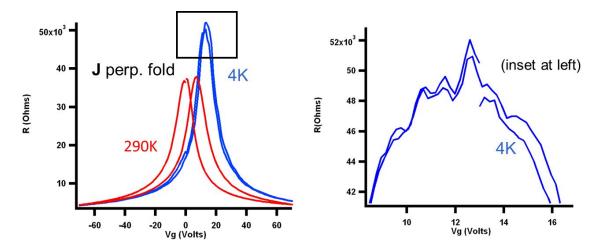

the gate field. As previously mentioned, metals are incompatible with this technique due to their high charge carrier concentrations and extremely short Debye screening lengths. However, other contact materials – semimetals and light- to medium-doped semiconductors – may allow penetration of the gate field. However, for optimal device performance, these materials must also have very low sheet resistances. In order to extend the SFPV structure to arbitrary materials, we need to consider dimensional confinement in directions *other* than out of plane (ultrathin).

So far, we have only constrained the contact material in the z direction (perpendicular to the plane of the semiconductor surface), which leaves us to consider the x and y in-plane dimensions. If we suffiently confine top contacts in either the x or y direction, one might expect that an applied gate field could exert some influence on the contact-semiconductor junction. As will be shown in the following section, confining the top contact dimension to be smaller than the bulk depletion width in the semiconductor allows the gate field to influence the contact-semiconductor junction, reminiscent of the action of a wave passing around a sub-wavelength obstruction. In this instance, the confined top contact may be composed of any material (even metals); a schematic is shown in figure 2.4.

Figure 2.4: SFPV using a "nanofinger" top contact (with a width less than the bulk depletion width of the semiconductor)

In the following section, we will consider both of these types of SFPV cell (both ultrathin and ultranarrow top contacts) theoretically and experimentally using Si as a prototypical semiconductor.

## 2.3 SFPV based on silicon Schottky junctions

To investigate the challenge of simultaneous electric contact to and carrier modulation of a semiconductor (using Si as a test case) via an applied electric field, we (1) solved a system of coupled equations using Matlab to simulate ultrathin (graphene) contact SFPV and (2) performed finite element simulations in COMSOL to simulate ultranarrow contact SFPV. For these test cases, we start by forming a Schottky junction solar cell (an alternative to the standard p-n junction), as the cells are relatively simple to both model and fabricate. A Schottky junction is formed between a metal

contact and a singly-doped semiconductor. As shown in figure 2.5, a large difference between the metal work function and the semiconductor's Fermi level causes charge transfer at the metal-semiconductor (MS) interface, forming a depletion layer and setting up an electric field to drive the drift current. Unfortunately, intrinsic Schottky junctions cannot produce open circuit voltages larger than half the semiconductor bandgap, and the MS interface has a very large recombination velocity. MIS cells solve these problems by introducing a tunnel insulator between the metal and semiconductor. The SFPV approach may solve these problems in a different way, by adding a potential barrier that increases open circuit voltage and reduces the recombination velocity.

Figure 2.5: Schottky junction band diagram for a metal contact to a n-type semiconductor. The differences in semiconductor and metal work function ( $\phi_s$  and  $\phi_m$ ) result in charge transfer and band bending at the MS interface.

## 2.3.1 Ultrathin contact (graphene) SFPV

Graphene is an attractive choice for an ultrathin SFPV top electrode. It is very transparent yet reasonably conductive as mentioned above, makes Schottky contact to both n- and p-type Si [16, 62], and allows electric fields to effectively partially penetrate it and influence underlying semiconductors, thus allowing for simultaneous gate-induced carrier modulation, electrical contact, and light transission. To simulate graphene top contact SFPV, we solve the following system of coupled equations:

- 1.  $Q_{gr}/A = D_{gate} D_{surf}$

- 2.  $\chi_{gr} = \chi_{cnp-gr} + \hbar v_F |Q_{gr}/q|^{1/2} \text{sign}(Q_{gr})$

- 3. Satisfy the drift-diffusion-Poisson equations in the Si, where  $\chi_{gr}$ 's effect on the boundary affects  $D_{surf}$ .

Here  $Q_{gr}$  is the graphene charge,  $D_{gate}$  and  $D_{surf}$  are the D-fields in the gate and at the surface of the silicon, and  $\chi_{gr}$  and  $\chi_{cnp-gr}$  are the work function of the graphene modified by the gating and at the charge neutral point, respectively. The work function of the graphene (determined by the charge in the graphene via the graphene density of states) determines the Schottky barrier height (via the Schottky-Mott equation). The charge in the graphene is determined by the charge in the gate and semiconductor space-charge region (these three must sum to zero). The Schottky barrier height, applied voltage, and gate voltage determine the total charge in the semiconductor space-charge region. When these equations are solved self-consistently, one is able to determine the effective Schottky barrier height as a function of applied gate voltage. Using the Schottky-Richardson equation, one is able to determine the current as a function of gate voltage (and thus the photovoltaic performance).  $\chi_{cnp-qr}$ is approximated as 4.6 eV [108]. Other parameters for the simulation were silicon type and doping (n-type,  $N_D \sim 1.1 \times 10^{16} \text{ e}^{-/\text{cm}^3}$ ), electron and hole carrier mobility lifetimes of 100 µs, and crystalline silicon properties obtained from Sze's Physics of Semiconductor Devices [95]. Bilayer graphene is treated similarly, as two monolayer graphene sheets with their own separate work functions. Multi-layer graphene is treated as the limit of infinitely many sheets. These simulations ignore certain parameters such as the limiting effects of sheet resistance (important for thinner graphene contacts) and transparency (an issue for very thick graphene contacts), as significant strides are being made by many other research groups to optimize graphene as a transparent electrode [67, 86, 96, 113].

Results of these simulations (performed in Mathematica) are shown below. Figures 2.6 and 2.7 show the Si potential profile (for saturated gate, indicated by the dashed line in figure 2.7) and the Schottky barrier height as a function of gate charge ( $Q_{gate}$ ). Limiting efficiencies as a function of gate charge are shown in figure 2.8.

As seen in figure 2.8, monolayer graphene performs quite well, achieving limiting efficiencies of up to  $\sim 19\%$ , as it permits the most field penetration. In realistic cells, the high series resistance of the monolayer graphene would have to be mitigated with additional metal busbars or by heavy graphene doping, though the large gate field effectively puts graphene into a highly-doped regime.

Having demonstrated high performance theoretically, we then fabricate and test experimental prototypes. We start by growing chemical vapor deposited graphene, as discussed later in chapters 3 and 4. Monolayer graphene is transferred from its Cu growth substrate to n-type Si ( $N_D \sim 10^{16} \, {\rm e^-/cm^3}$ ), with a total active cell area of about 0.04 cm², large enough to neglect the added active area due to the large ( $\sim 100 \, \mu m$ ) minority carrier diffusion length in low-doped crystalline Si. The graphene is contacted with evaporated Cr/Au, and bottom contact to the Si is made by thermally evaporating Al. A gate is applied using 1-ethyl-3-methylimidazolium bis (trifluoromethylsulfonyl)imide ionic liquid (EMI-BTI, Sigma Aldrich No. 11291). Current-voltage curves as a function of gate voltage ( $V_g$ ) are seen in figure 2.9, with an inset showing a picture of the device. The graphene was held at ground and a bias

Figure 2.6: Potential in Si with saturated gate ( $Q_{gate} \sim 1.5 \times 10^{13}~e^-/cm^2$ ) for monolayer, bilayer, and multi-layer graphene.

Figure 2.7: Schottky barrier height versus  $Q_{gate}$  for monolayer, bilayer, and multi-layer graphene.

Figure 2.8: Efficiency versus  $Q_{gate}$  for monolayer, bilayer, and multi-layer graphene. The dashed line at  $Q_{gate} \sim 1.5 \times 10^{13} e^{-}/cm^{2}$  shows the gating used in figure 2.6. (from [82])

voltage (applied to the bottom electrode) was swept while the gate is held at a fixed voltage. Details of the measurement process and testing apparatus are found in the appendix (A.1).

Negative gate voltage repels electrons and attracts holes to the top of the n-type Si and graphene, notably enhancing  $V_{OC}$ , short circuit current  $(I_{SC})$ , and fill factor (FF). With the application of a modest gate voltage (which consumes negligible power due to the  $\sim$  nA gate leak current) of  $V_g = 1.2$  V, power conversion efficiency (PCE) increases from  $\sim 1.5\%$  to  $\sim 1.8\%$ . A variety of factors are likely keeping us far from the efficiency limits predicted by theory, including the high graphene series resistance, gate transparency, and the lack of an antireflection coating or surface texturing. To investigate the performance of graphene "bilayers," we transferred another graphene monolayer onto the existing monolayer graphene on silicon cell. Again, we applied a gate with an ionic liquid, and current-voltage curves as a function of gate voltage (labels) are shown below in figure 2.10.

For the bilayer cell, performance increases with increasingly negative  $V_g$ , as seen for the monolayer. However,  $V_{OC}$  and the ultimate performance of the cell are consistently lower than that seen for the monolayer case; this may be due to the shielding of the gate electric field by folds introduced during transfer of the second monolayer. The effectiveness of the gating quickly diminishes with increasing graphene layers. Since the performance of many-layer graphene on Si has already been extensively

Figure 2.9: Current-voltage curves versus gate voltage for monolayer graphene silicon SFPV cell (AM1.5), with an inset showing an optical micrograph of the cell. (from [82])

Figure 2.10: Bilayer graphene SFPV cell performance as a function of gate voltage (AM1.5). (from [82])

studied in the literature [62], we did not repeat the test with thicker graphene using additional transferred monolayers.

These results show that graphene can serve as an effective ultrathin SFPV contact. No known metals would be compatible with this ultrathin geometry, as the screening length is significantly shorter than the minimum viable thickness for a continuous metal sheet. Low-doped semiconductors may be compatible with this approach, though it may be challenging to simultaneously achieve low carrier concentration and low sheet resistance.

We will now consider additional contact confinement strategies that are compatible with a wide range of contact materials, not just graphene and low-doped semiconductors but high carrier concentration materials such as metals.

#### 2.3.2 Nanofinger SFPV: ohmic and Schottky contacts

Graphene is not an ideal rectifying contact for many semiconductors, so it would be beneficial to have strategies to use other materials (metals, highly-doped semiconductors, etc) for SFPV cells. By constraining at least one of the in-plane dimensions of the top contact, this is in fact possible for arbitrary contact materials.

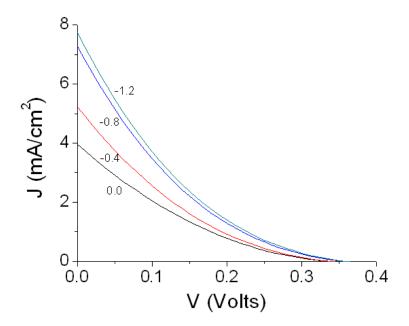

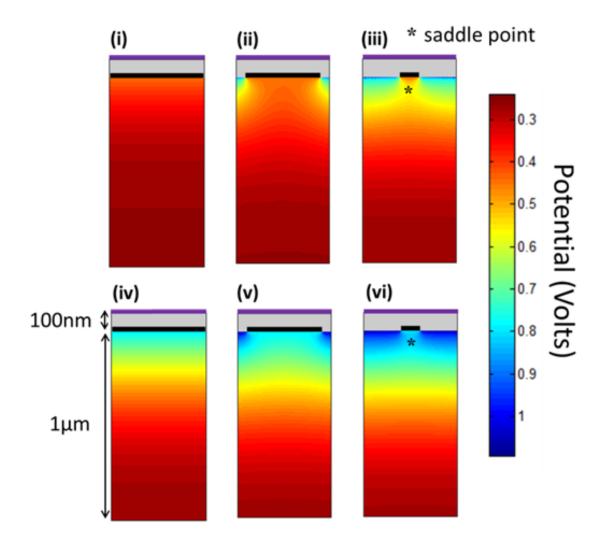

To theoretically consider the performance of these "nanofinger" SFPV cells, we performed finite-element simulations in COMSOL to solve the drift-diffusion-Poisson The simulations are two dimensional (extruding nanofingers infinitely into the third dimension) and have periodic boundary conditions (assuming equallyspaced nanofingers). The Poisson equation is satisfied in the semiconductor and gate dielectric, and the top, bottom, and gate metal contacts define the boundary conditions. The Crowell-Sze model is used to determine majority carrier transport at the metal-semiconductor Schottky barriers [23], and image-force lowering of the barrier is modeled by self-consistently modifying the contact work function based on the local electric field [95]. To simplify simulations, recombination at the bottom contact is set to zero (assuming passivation with a back-surface field). AM1.5 illumination was used, and the silicon absorption coefficient was set at  $\alpha = 3 \times 10^3$ /cm. As in the graphene simulations, carrier lifetimes were set at 100 µs (assuming only Shockley-Read-Hall recombination). Other material properties used include the following: silicon type (n), carrier density  $N_D = 10^{15} e^{-/cm^3}$ , wafer thickness  $D = 10 \mu m$ , and depletion width  $d = 1 \mu m$  (determined by  $N_D$ ); gate dielectric properties (thickness t = 100 nmand dielectric constant  $\kappa = 3.9$ ); and contact properties (work function  $\phi$  (4.45 eV for ohmic and 4.8 eV for Schottky contacts), width w, and center-to center separation s). We only consider silicon Schottky contacts, and there is room for considerable exploration with other cell types such as MIS, semiconductor-insulator-semiconductor (SIS), and perhaps even partially chemically-doped cells, as will be discussed near the end of this chapter.

Results of our simulations of nanofinger SFPV are seen in figure 2.11, with planar  $(w = \infty)$ , w = 400 nm, and w = 100 nm wide ohmic (i-iii) and Schottky (iv-vi)

contacts to the n-type Si.

Figure 2.11: Simulated potential plots for ohmic and Schottky nanofinger SFPV. (from [82])

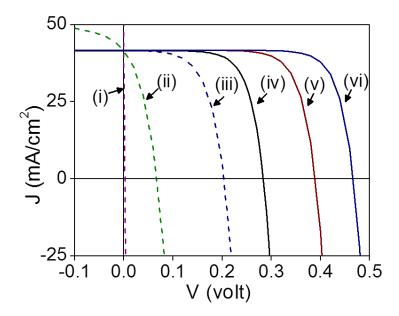

In the simulation, fingers are held at ground and the gate is fixed at a large negative voltage (-10 V), which is sufficient to saturate the effect and make the choice of gate metal work function arbitrary. As expected, wide fingers (i,iv) screen out the effect of the gate completely, but sufficiently narrow fingers (iii,vi) permit the formation of an added potential barrier underneath the electrode. Majority carriers are blocked by this added barrier and are forced to flow around to the strongly-gated sides of the contact. Thus, this added barrier can increase the effective Schottky barrier height, lowering the diode saturation current and improving open circuit voltages and efficiencies. Corresponding current-voltage curves for these six cells are seen in figure 2.12.

Figure 2.12: Current-voltage curves for the ohmic and Schottky SFPV devices in figure 2.11. (from [82])

We repeated these simulations for a range of finger widths, from planar down to w = 10 nm, and plotted the open circuit voltages and efficiencies in figure 2.13.

The observed performance increases greatly exceed that expected by simply reducing contact areas (which reduces recombination current) [39]. Effective gating is seen for finger widths well below the bulk semiconductor depletion width (in this case,  $d=1~\mu m$ ), which is as one might expect since d is the distance over which potentials can vary in the semiconductor. Forward bias and the intrinsic Schottky barrier height are also important factors influencing the resulting added potential barrier formation. We see that, given sufficiently narrow fingers, the effect is strong enough to form a large potential barrier below ohmic contacts, raising efficiencies from 0% up to about 8% for w=10~nm.

Finally, we also consider the effect of finger separation (s). The above results were obtained for  $s=10~\mu m$ , as this seemed to be a realistic middle ground for balancing light transmission and sheet resistance. Using a fixed finger width w=100nm, we simulated the effect of a changing finger spacing s, and resulting efficiencies and open circuit voltages are shown in figure 2.14.

Decreasing the spacing increases saturation current and shading but also decreases series resistance. Since we don't consider shading or series resistance in these simulations, only the effect of changing saturation current is seen, with larger spacing resulting in higher performance.

Figure 2.13: Maximum efficiency and  $V_{OC}$  for ohmic and Schottky nanofinger SFPV. (from [82])

Figure 2.14: Effect of finger spacing on SFPV performance (finger width fixed at 100nm). (from [82])

#### Experimental nanofinger silicon SFPV using ohmic contacts

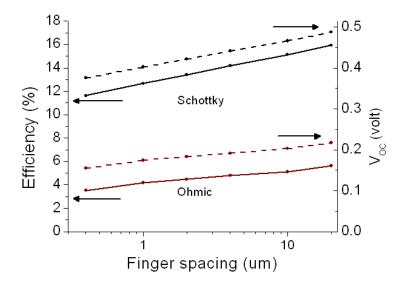

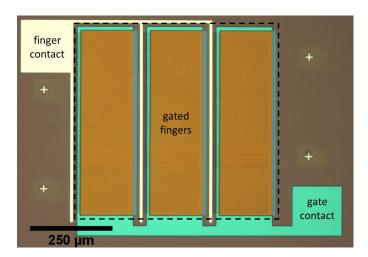

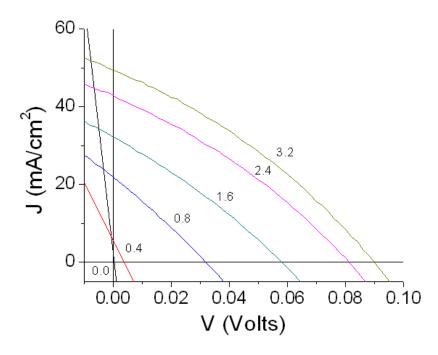

To validate these models, we next fabricated and tested experimental prototypes. First, to isolate the SFPV effect from improvements due to better surface passivation, we fabricate silicon SFPV cells with intrinsically ohmic (annealed Al) 250 nm wide contacts to p-type ( $N_A \sim 1 \times 10^{16}/cm^3$ ), with a similar w/d ratio to the device seen in part ii of figure 2.11. The finger spacing is set at 5 µm, which (as we have shown) should not greatly diminish performance. An optical image of the resulting cell is shown in figure 2.15. Gating is achieved with 150 nm of electron-beam evaporated SiO<sub>2</sub> and a ~40% transparent Cr/Au gate contact. Current-voltage plots as a function of gate voltage ( $V_q$ ) are shown in figure 2.16 (AM1.5 illumination).

Figure 2.15: Optical micrograph of (ohmic) Al nanofinger silicon SFPV cell. The active area is outlined with a dashed line. (Note: This device has an ITO top gate, not Cr/Au as tested for figure 2.16.)

As we did previously with graphene SFPV cells, the partially-screening contact is fixed at ground while bias voltage on the bottom contact is varied. Positive gating repels holes and attracts electrons to the top of the p-type Si, causing inversion between fingers and eventually adding an extra potential barrier underneath the contacts. The initially ohmic behavior (a straight IV curve through the origin) is tuned into a slightly Schottky contact, and open circuit voltage  $(V_{OC})$ , short circuit current  $(I_{SC})$ , fill factor (FF), and shunt resistance  $(R_{shunt})$  increase monotonically with stronger gating. PCE increases from 0% to  $\sim 1.4\%$  (with  $V_{OC} \sim 0.09$  V) with  $V_q$ = 3.2 V, near our model's predictions. We should note that this cell is far from optimized, and performance may be improve through better gate transparency and thickness, dielectric quality, antireflection coatings, and surface texturing. The gate field requires minimal power to maintain (several orders of magnitude below the cell's generated power), as the gate contact draws only 6 nA at the highest applied  $V_q$ . We note that this particular cell area was rather small (600  $\mu$ m  $\times$  600  $\mu$ m), so a 100  $\mu$ m carrier diffusion length may reduce real cell efficiencies by up a multiplicative factor of 0.56. However, regardless of this correction, the SFPV effect is still shown to be distinct from surface passivation.

Figure 2.16: Current-voltage curves for ohmic nanowire SFPV (AM1.5) (from [82])

Of course, as our model suggests, we can expect to attain much higher cell efficiencies by starting with Schottky contacts.

#### Experimental nanofinger silicon SFPV using Schottky contacts

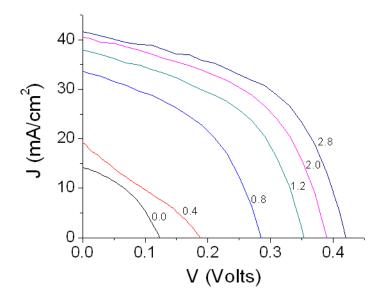

We repeated the fabrication steps above using Schottky contact (Cr) to the p-type silicon ( $N_A \sim 3 \times 10^{15}/\text{cm}^3$ ). For these cells, w = 300 nm (similar to part v of figure 2.11) and the cell area was 200 µm × 200 µm. All other parameters were identical to the ohmic silicon SFPV cells in the previous section. Current-voltage curves for positive gating are shown in figure 2.17. Again, the nanofinger is fixed at ground, the gate is fixed at various voltages, and bias voltage on the bottom contact is swept for each fixed gate voltage. As with the ohmic case, positive gating causes inversion between fingers and adds an extra potential barrier underneath the contacts, improving  $V_{OC}$ ,  $I_{SC}$ , FF, and efficiency.

In the positive gating regime, efficiency for these cells is increased from  $\sim 0.7\%$  (V<sub>g</sub> =0.0 V) to  $\sim 9\%$  (V<sub>g</sub> =2.8 V). The small area may reduce the efficiency by a factor of 4 (given L<sub>e</sub>  $\sim 100 \ \mu m$ ).

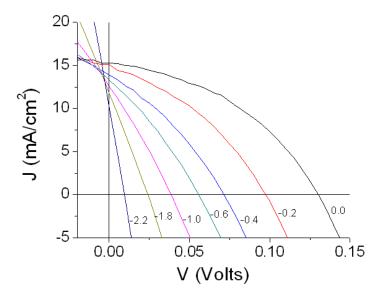

Just as an ohmic contact can be made rectifying, a Schottky contact may be made ohmic. We demonstrate this by gating the Schottky SFPV device with a negative voltage, thus attracting holes and repelling electrons from the top of the semiconductor. As seen in figure 2.18, a sufficiently negative gate voltage is able to shrink the

Figure 2.17: Current-voltage curves for Schottky nanowire SFPV: positive gating (AM1.5 illumination). (from [82])

depletion region to the point at which there is effectively no barrier. This flexibility may offer some interesting opportunities for improving non-ideal ohmic contacts.

Figure 2.18: Current-voltage curves for Schottky nanowire SFPV: negative gating (AM1.5 illumination) (from [82])

So far we have shown the versatility of the SFPV design, with multiple possible geometries (ultrathin or ultranarrow contacts) and tuning strategies (ohmic to Schottky, Schottky to more Schottky, Schottky to ohmic, and high resistance ohmic to low resistance ohmic). Additionally, we have shown that the power consumed by the gate will be negligible compared to generated photovoltaic power. However, practical (commercial) photovoltaic devices require simplicity and low cost, and adding a third, powered electrode may seem like a recipe for disaster. In the next section, we will discuss how we solved this problem and effectively removed the need for an isolated, third electrode.

## 2.4 Self-contained gating for practical SFPV cells

The SFPV gate electrode introduces a few complications. For one thing, the need for external batteries will increase the cost and complexity (without even considering increased failure rates for panels as batteries die) of cells and panels. Furthermore, modules are typically made by connecting many cells in series; this would mean that local grounds would increase for every cell in the string, and gate voltages must track these grounds appropriately. Fortunately, we devised a simple way to power this third electrode internally and in a way which tracks the local ground.

#### Self-gating feedback loop

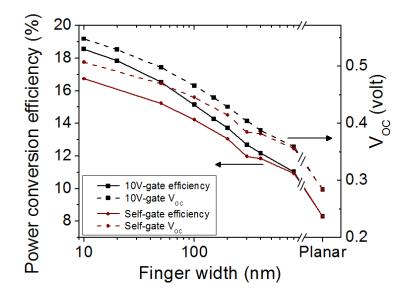

If we connect the cell output directly to the gate, the gate can be self-powered and have an appropriately floated ground. The power drawn by the gate is negligibly small compared to the photo-generated power, and the typical operating voltage of a Schottky or heterojunction cell (0.1–1 V) can be sufficient to produce an impactful gate field. Self-gating thus sets up a feedback loop, which increases the cell operating voltage from the intrinsic heterojunction operating voltage to a higher level, given careful choices of gate metal, gate dielectric material and thickness, and porous top electrode (which forms an initially Schottky or heterojunction contact). To model this self-gating effect, we repeated our previous simulations using a thin gate dielectric and appropriately chosen gate metal (with work function outside of the band gap). As shown in figure 2.19, given careful choices of gate contact and dielectric, self-gating can achieve nearly the same efficiencies as those achieved with a saturated, externally-powered gate.

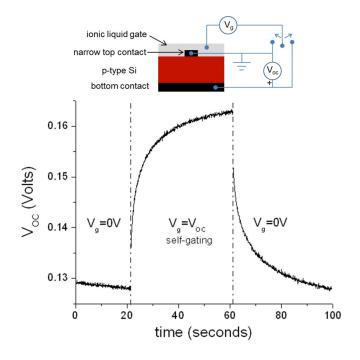

We experimentally demonstrated self-gating using a SFPV cell with with 250 nm wide Schottky (Cr) contacts to  $N_A \sim 3 \times 10^{15}~e^-/cm^3$  p-type Si and an EMI-BTI ionic liquid gate. Figure 2.20 shows  $V_{OC}$  versus time while the gate is toggled between ground and the cell output; illumination is AM1.5. We see a significant and reversible increase of about 30% in  $V_{OC}$  over the non-gated Schottky barrier configuration and a  $\sim 60\%$  increase in photoconversion efficiency.

Figure 2.19: Simulation of self-gating performance versus finger width for Schottky SFPV (from [82])

Figure 2.20: Experimental demonstration of self-gating feedback loop. After toggling the gate to  $V_{OC}$ ,  $V_{OC}$  increases significantly. (AM1.5 illumination) (from [82])

Additionally, this gating may also be achieved through the use of dielectrics, electrolytes, ferroelectrics, or other materials with fixed surface charges or polarizations, as will be discussed in the following section.

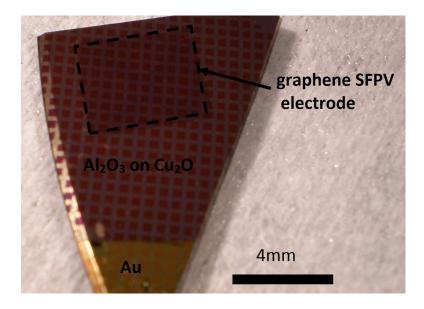

#### Gating via fixed charge or polarization

Besides metal-dielectric gates, there are other ways to generate local electric fields. Some dielectrics can have a large fixed charge (either positive or negative) at the interface with other materials. For instance, as shown in table 2.2,  $Al_2O_3$  deposited by atomic layer deposition (ALD) has been demonstrated to hold up to  $10^{12}-10^{13}e^-/cm^3$ , sufficient to passivate highly doped Si and enough to invert medium-doped Si  $(10^{14}-10^{16}~e^-/cm^3)$  [1, 85]. Additionally, materials such as ferroelectrics can be poled to have large built-in polarizations, equivalent to a very large fixed surface charge [109]. Such materials enable SFPV cells without the added complexity of a powered gate. Further, they do not require metal gate contacts, which can reduce light transmission into the cell, and are themselves transparent and can be tailored to be reasonable single-layer antireflection coatings. As such, they are likely the easiest and most commercially-viable long-term solution for implementing SFPV cells.

| Si bulk doping $(e^{-}/\text{cm}^{3})$ | Areal charge density for inversion $(e^{-}/\text{cm}^{2})$ |  |

|----------------------------------------|------------------------------------------------------------|--|

| $10^{14}$                              | $3 \times 10^{10}$                                         |  |

| $10^{15}$                              | $1 \times 10^{11}$                                         |  |

| $10^{16}$                              | $3 \times 10^{11}$                                         |  |

| Fixed charge/polarization material        | Maximum areal charge density $(e^{-}/\text{cm}^{2})$      |

|-------------------------------------------|-----------------------------------------------------------|

| $Al_2O_3$ (ALD)                           | $10^{12} - 10^{13} [1, 85]$                               |

| Si <sub>3</sub> N <sub>4</sub> (Cs-doped) | $2-3\times10^{12} [26]$                                   |

| P(VDF-TrFE) (ferroelectric)               | $6 \times 10^{13} \text{ (using 0.1 C/m}^2\text{) [109]}$ |

Table 2.2: Areal charge density for inversion as a function of Si bulk doping (derived using depletion widths from Mott-Schottky relation), as compared with areal fixed charge density in various dielectrics and ferroelectrics. [1, 26, 85, 109].

## 2.5 Criteria for promising SFPV semiconductors

The true benefit of the SFPV cell structure, in addition to avoiding the damage and cost of traditional chemical doping, is that it can be applied to virtually any semiconductor. While silicon Schottky junction SFPV cannot attain the efficiencies of doped Si photovoltaic cells, SFPV structures made with other types of silicon photovoltaics (e.g. MIS) and various heterojunctions made with other materials may be

able to perform at commercially interesting efficiency levels. In addition to semiconductor stability (for example, FeS<sub>2</sub> may be corrode and leach sulfuric acid ( $H_2SO_4$ ) in the presence of moisture), one key criterion for useful SFPV materials is the semiconductor's bulk depletion width, as determined by its carrier concentration and dielectric constant. More heavily doped semiconductors ( $> 10^{17} e^-/cm^3$ ) will require stronger electric fields to achieve inversion, and at some point dielectric breakdown will occur before you can apply a sufficiently strong electric field. Additionally, heavily doped semiconductors will have smaller depletion widths, and useful widths for SFPV nanofinger contacts will become vanishingly small. Fortunately, there are still many semiconductors which have low to medium doping and are feasible for SFPV cells. Some promising semiconductors are listed below in table 2.3.

| Material           | Bandgap (eV)                     | Carrier concentration (e <sup>-</sup> /cm <sup>3</sup> ) |

|--------------------|----------------------------------|----------------------------------------------------------|

| $Zn_3P_2$          | 1.4–1.5 (direct)                 | $10^{15} - 10^{17} \text{ (p)}$                          |

| $\mathrm{Sb_2S_3}$ | 1.7 (direct)                     | $\sim 10^{12} \text{ (n)}$                               |

| SnS                | 1.2–1.3 (direct), 1.0 (indirect) | $10^{14} - 10^{15} \text{ (p)}$                          |

| $\mathrm{Cu_2O}$   | 2.1 (direct)                     | $10^{13} - 10^{15} \text{ (p)}$                          |

| CdTe               | 1.5 (direct)                     | varies (p)                                               |

| CIGS               | 1.0–1.7 (tunable, direct)        | varies (p)                                               |

| CZTS               | 1.0–1.5 (tunable, direct)        | varies (p)                                               |

| amorphous Si       | 1.7 (direct)                     | varies (n,p)                                             |

| crystalline Si     | 1.1 (indirect)                   | varies (n,p)                                             |

| GaAs               | 1.42 (direct)                    | varies (n,p)                                             |

| InP                | 1.35 (direct)                    | varies (n,p)                                             |

Table 2.3: A few candidate materials for SFPV cells. Three rough classes of materials are listed. The first group (phosphides, sulfides, oxides) represents the "new" materials that are incompatible with chemical doping and form poor heterojunctions. The second group (CdTe, CIGS, CZTS) can already form reasonably good p-n heterojunctions but may be improved by the SFPV design. The third group (cSi, GaAs, InP) includes materials that can be successfully chemically doped to form high efficiency solar cells but may be cheaper to make (or attain higher efficiencies) using the SFPV geometry in conjunction with mild doping, heterojunctions, or MIS configurations. Sources for these data are as follows: Zn<sub>3</sub>P<sub>2</sub> [9, 55], Sb<sub>2</sub>S<sub>3</sub> [14, 84], SnS [43, 73, 88], Cu<sub>2</sub>O [10, 70], and CZTS [4].

We have explored this effect with earth-abundant  $Cu_2O$  and are considering other such materials (SnS and  $Zn_3P_2$ ).

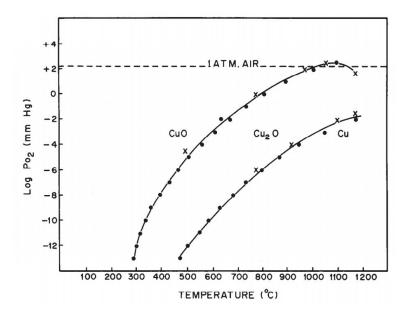

#### 2.5.1 Cuprous oxide

To demonstrate the universality of the SFPV effect, we studied  $Cu_2O$ , a hard-to-dope, earth-abundant semiconductor often touted as a high potential (up to 20% conversion efficiency), low-cost PV material [70]. As seen in 2.3, the doping range puts  $Cu_2O$  well within the range of feasibility for SFPV devices.

Before constructing experimental prototypes, we first modeled the system using COMSOL finite element simulations (used previously for silicon nanofinger SFPV) to estimate the potential for Cu/Cu<sub>2</sub>O Schottky junction SFPV cells. Cu is known to form a fairly large Schottky barrier with Cu<sub>2</sub>O, and tends to form at the surface of most metal-Cu<sub>2</sub>O junctions (as most other low work function metals, needed for high barrier Schottky contacts, will be oxidized by the Cu<sub>2</sub>O and leave a layer of reduced Cu). Parameters used for the simulation include the following: SiO<sub>2</sub> properties used in silicon SFPV simulations and thickness of 100nm, Cu<sub>2</sub>O properties (p-type doping with N<sub>A</sub>  $\sim 10^{14}$ /cm<sup>3</sup>, minority carrier lifetime  $\sim 1$  µs, E<sub>g</sub>  $\sim 2.2$  eV,  $\alpha \sim 3 \times 10^5$ /cm, thickness = 10 µm), and Cu contact separation of 2 µm. This doping level results in a depletion width of about 1 µm, so a contact width of 300 nm wide should allow for effective gating. Results for these simulations are shown in table 2.4.

| Cell              | $V_{OC}(V)$ | $I_{SC} (mA/cm^2)$ | Efficiency (%) |

|-------------------|-------------|--------------------|----------------|

| planar            | 0.6         | 5.1                | 1.7            |

| SFPV (w = 300 nm) | 0.79        | 7.8                | 3.9            |

Table 2.4: Cu/Cu<sub>2</sub>O planar and SFPV simulations.

As seen in the table, the SFPV geometry is able to more than double in efficiency. In fact, this may not be the limit of attainable efficiencies, as the same SFPV cell achieved  $\sim 10\%$  higher efficiencies (above 4% absolute) when doping was increased to  $3\times 10^{14}/{\rm cm}^3$ .

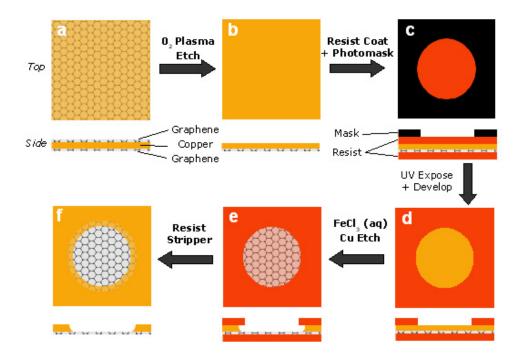

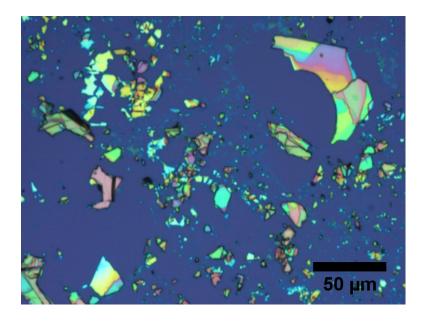

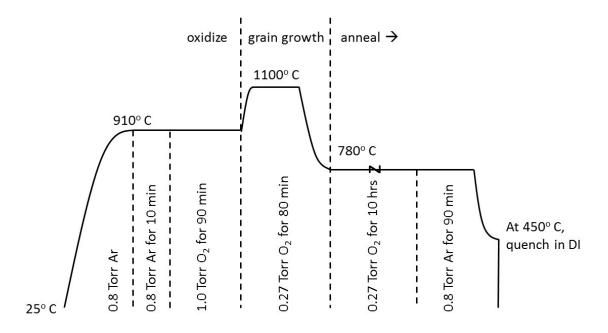

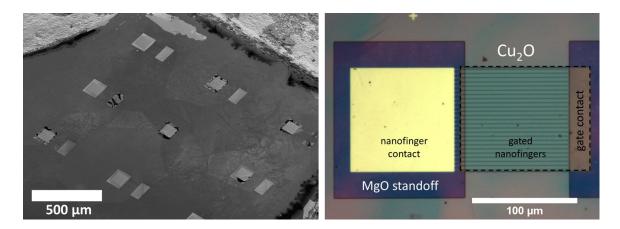

Motivated by this result, we created nanofinger  $\mathrm{Cu_2O}$  SFPV cells. Instead of using  $\mathrm{Cu}$ , we used indium tin oxide (ITO) contacts, as this has been shown to achieve higher  $\mathrm{V}_{OC}$ ; because the ITO is already an oxide, a layer of reduced  $\mathrm{Cu}$  does not form and limit the barrier height as seen with low work function metals. Thermal oxidation is used to convert  $\sim 100\text{-}250~\mu\mathrm{m}$  thick  $\mathrm{Cu}$  foils (Puratronic, Alfa Aesar No. 42974) into polycrystalline  $\mathrm{Cu_2O}$  wafers. These are then mechanically polished and chemically treated (using 2 vol%  $\mathrm{Br_2\text{-}MeOH}$  at room temperature for 2 minutes) right before contact deposition to avoid a surface layer of  $\mathrm{CuO}$  or other undesirable decomposition products. Full details of the  $\mathrm{Cu_2O}$  growth can be found in chapter 5.

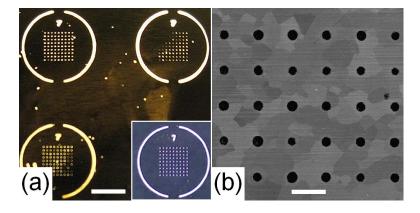

Heterojunctions are created using w = 750 nm ITO nanofingers (5 µm spacing) contacting the p-type  $\text{Cu}_2\text{O}$ . A top gate is formed with electron-beam evaporated MgO dielectric (125nm) and sputtered ITO (40nm). Silver epoxy (Epotek H20E) is used to make ohmic contact to the bottom of the  $\text{Cu}_2\text{O}$ . Efficiency enhancement

(AM1.5 illumination) versus gate voltage is seen in figure 2.21, with an optical image of the device shown as an inset. A fairly small  $V_g$  (20mV) improves the efficiency by a factor of nearly 1.6. Our absolute efficiencies are quite small ( $\sim 10^{-5}\%$ ) likely due to the high reactivity of the Cu<sub>2</sub>O surface to moisture, which is known to drastically reduce  $V_{OC}$ . However, if applied to optimized devices (higher mobility Cu<sub>2</sub>O with a non-damaged surface), the SFPV architecture may enable much higher efficiencies than present world records and make Cu<sub>2</sub>O interesting for commercial PV cells or at least some electronics applications (e.g. 2.1eV laser diodes).

Figure 2.21: Efficiency enhancement versus gate voltage for  $Cu_2O$  SFPV cells, with an optical image of the device shown as an inset. (from [82])

#### 2.5.2 Other candidate materials in progress

Besides  $Cu_2O$ , we are considering several other abundant oxides, phosphides, and sulfides for SFPV cells. Two of the most interesting materials, as shown in table 2.3, are SnS and  $Zn_3P_2$ .

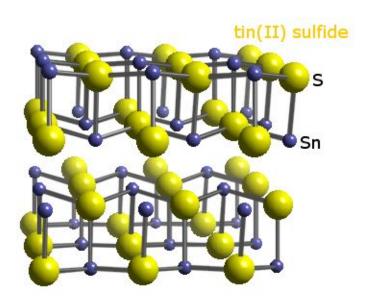

#### Tin (II) sulfide

SnS has an orthorhombic crystal structure (seen in figure 2.22), with weak van der Waals bound bilayer planes stacked in the c direction. Like graphite and other weakly bound layered systems, crystalline SnS can be exfoliated to produce large, atomically-flat surfaces.

Figure 2.22: SnS crystal structure. Source: webelements.com

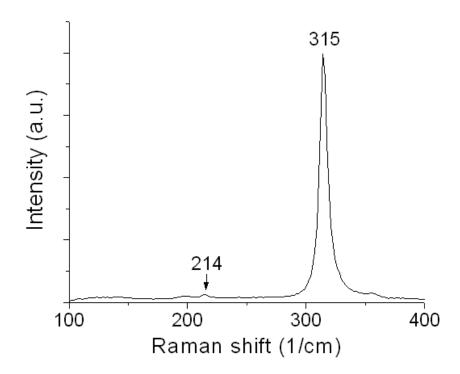

SnS has an indirect gap at 1.0 eV and a direct gap around 1.2--1.3 eV, allowing it to achieve > 25% PV efficiency. Single crystals of SnS have been grown with reasonable resistivity ( $120 \Omega$ -cm) and high in-plane (perpendicular to the c-axis) mobility of  $34 \text{ cm}^2/\text{V-s}$  [43]. Efficiencies of up to 1.3% have been obtained using chemical spray pyrolysis grown SnS [80], and it stands to reason that higher crystallinity samples should enable higher performance efficiencies. This paper used a SnO<sub>2</sub> ohmic and In-doped CdS heterojunction contact, but other reports have suggested that In and (non-annealed) Al make good ohmic and Schottky contacts, respectively.

To investigate the potential of SnS SFPV cells, we grew SnS via vapor phase transport (details in chapter 5) and exfoliated the resulting single crystals onto  $\mathrm{SiO}_2/\mathrm{Si}$  substrates. Cleaving reveals large, smooth, pristine planes, as seen in figure 2.23. This image also shows a schematic of a possible SFPV cell, with an In microsoldered ohmic contact and Al nanofingers (on which a top gate could be applied), which exploits the high SnS in-plane mobility. Such cells would likely have low  $\mathrm{I}_{SC}$ , as exfoliation tends to produce submicron thickness sheets. However, these cells could be tested at higher illuminations to simulate complete absorption of AM1.5 sunlight. Dr. Oscar Vazquez-Mena and Onur Ergen are continuing this work in the Zettl lab.

Figure 2.23: Exfoliated tin sulfide single crystals on  $SiO_2$  and a schematic of a planned SFPV cell (In ohmic and Al nanofinger Schottky contacts). As noted in chapter 5, these crystals were revealed to be  $SnS_2$ , an indirect semiconductor with gap around 2 eV.

#### Future directions: Zinc phosphide, CdTe, CIGS

Zinc phosphide  $(Zn_3P_2)$  is another hard-to-dope but very promising PV material, with a direct bandgap of 1.5eV. Record efficiencies currently stand around 6%, using Mg Schottky contacts (which may alloy with the surface of the  $Zn_3P_2$  upon annealing) [9]. We plan to construct nanofinger SFPV cells using Mg/ $Zn_3P_2$  Schottky or Mg/(hBN or  $SiO_2$ )/ $Zn_3P_2$  MIS cells. Growth methods for high quality  $Zn_3P_2$  include vapor regrowth of stoichiometric ratios of Zn and P and molecular beam epitaxy. We have had some discussions with the Atwater research group at Caltech, experts in both these growth methods, to initiate collborations for  $Zn_3P_2$  SFPV cells.

SFPV cells may also offer benefits to commercial p-n heterojunctions, namely those formed between n-type CdS and p-type CdTe or  $CuIn_xGa_{1-x}Se_2$  (CIGS). CdTe and CIGS cells can currently achieve efficiencies in the high teens to low twenties, though they ought to be able to break 30%. Two problems with these cells include slightly non-ideal heterojunctions and parasitic absorption (absorption and nonradiative recombination) in the CdS. The SFPV geometry could address both of these issues by minimizing the area of CdS contact needed (by inverting the CdTe or CIGS in regions between the CdS) and increase the band bending that normally results from the junction with CdS. CdS is most often deposited on these cells by a chemical bath process. Due to the safety concerns in handling the waste that results from this bath process, we are considering alternate n-type materials such as bath-deposited

ZnS(O,OH) or sputtered ZnO. To make SFPV cells that could beat current industry costs, we would need a non-lithographic nanofinger contact deposition method such as electrospinning or spin-coating of premade nanowires and would also likely use a self-gating strategy with a fixed charge or polarization material.

#### 2.6 Conclusions and future work

Our new SFPV method has shown that careful choice of the top contact geometry enables formation of high quality, electric-field-induced semiconductor p-n junctions. It offers the benefits of MIS and field-induced junctions (energy savings and minimized damage from chemical doping) and also relaxes the limitation of top contact heterojunction or Schottky barrier heights and may allow many previously impossible p-n junctions to be constructed, namely those using difficult-to-dope compound semiconductors that may hold the key to making solar energy an affordable energy source. Since SFPV cells use thick dielectrics (~ 100nm) instead of 1-2nm thick tunnel oxides, SFPV cells may prove more robust than MIS cells.

Several SFPV projects continue in the Zettl group, led by Dr. Oscar Vazquez-Mena and Onur Ergen. A few promising SFPV projects in progress include the following:

- 1. MIS silicon cells repeating Si SFPV cell design with a SiO<sub>2</sub> or other tunnel insulator

- 2. SnS cells using vapor grown, exfoliated single crystals

- 3. Zn<sub>3</sub>P<sub>2</sub> or Cu<sub>2</sub>O in collaboration with Caltech's Atwater group

- 4. Improving commercial CdTe or CIGS cells by selectively removing contacts and gating with P(VDF-TrFE)

## Chapter 3

# Graphene and carbon nanomaterials

## 3.1 Background

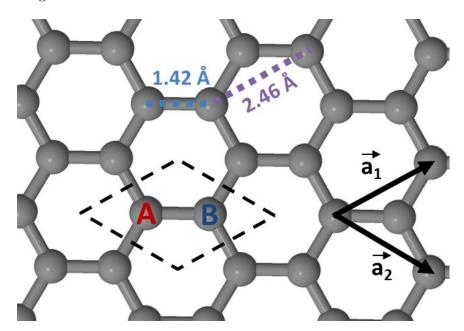

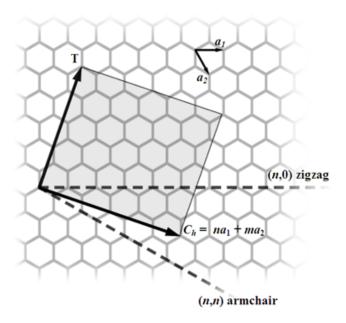

Graphene is an hexagonal 2D lattice of  $\rm sp^2$ -bonded carbon. The carbon-carbon bond length is 0.142 nm and the unit cell consists of two inequivalent sites, A and B, as shown in figure 3.1.

Figure 3.1: Graphene structure

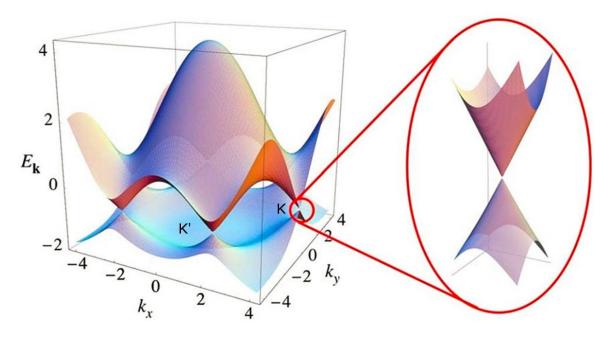

Graphene's band structure can be estimated with tight binding, as reported by P. R. Wallace [101]. The result is a Fermi surface consisting of six Dirac points (three

sets of inequivalent K and K' points) and a linear dispersion relation ( $E = \hbar v_F k$ ) at small energies around the Dirac points, as shown in figure 3.2 [12, 101].

Figure 3.2: Band structure of graphene [101] (image from Castro-Neto et al. [12])

This unusual band structure, which results in charge carriers behaving as relativistic massless Dirac fermions with an effective "speed of light" of  $\sim c/300~(10^6~{\rm m/s})$ , leads to many of graphene's unique properties. Graphene's low density of states near the Dirac point makes it highly tunable with applied electric fields, as was shown in chapter 2 and will be discussed more fully in chapter 4.

## 3.2 Graphene growth by CVD

Novoselov and Geim's exfoliation techniques resulted in very low yields, typically at best a few 10 µm sized flakes per cm<sup>2</sup> Si wafer. Fortunately, a highly scalable and simple monolayer graphene growth method – chemical vapor deposition (CVD) – was developed in 2009. This was first demonstrated by the Ruoff group, using Cu as a growth substrate [63]. Hydrocarbons are flowed over the Cu substrate, which is maintained at a high temperature (enough to crack the hydrocarbon). The hydrocarbon, typically methane, adsorbs on the Cu, cracks, and graphitizes. Cu has a very low carbon solubility, and as a result only the cracked C is forced to remain on the surface until it graphitizes. Higher carbon solubility transition metals, such as Ni and Fe, result in the formation of few- or many-layer graphene [83]. In the Ruoff process, methane (CH<sub>4</sub>) and a small amount of hydrogen (H<sub>2</sub>) is flowed over

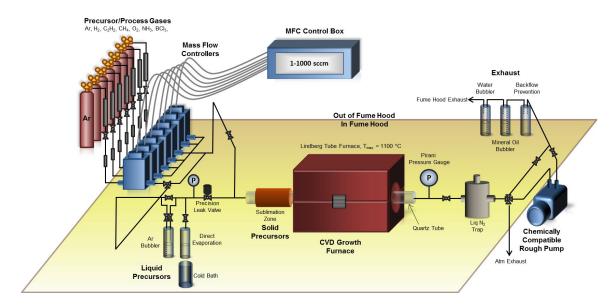

Figure 3.3: A picture of the carbon CVD system used for graphene and carbon nanotube synthesis. A quartz tube sitting in a furnace holds the growth substrate; gases enter the tube through the steel lines on the left and exhaust to a vacuum (or bubbler, for atmospheric pressure recipes) on the right.

Cu at  $950^{\circ}\text{C}$   $-1040^{\circ}\text{C}$  for 1-30 minutes. This can be performed at a reduced pressure (10 mTorr -5 Torr) or at atmospheric pressure; in the latter case, a carrier gas such as argon is used and flow rates are increased from a few tens of sccm to hundreds of sccm.

Following the first published CVD growth recipe, my early growth recipes used a simple ramp to  $1000^{\circ}$ C in 10 sccm  $H_2$  (to reduce and then prevent re-oxidation of the Cu substrate), followed by a 20 minute growth at  $1000^{\circ}$ C with 10 sccm  $H_2$  and 40 sccm  $CH_4$ . A picture of the Lindberg Blue Mini Mite growth furnace is seen in figure 3.3. After growth, the tube and graphene-covered Cu were cooled to  $\sim 25^{\circ}$ C while flow rates for the methane and hydrogen gases were maintained. Such growth procedures resulted in grain sizes on the order of  $1 \mu m$ .

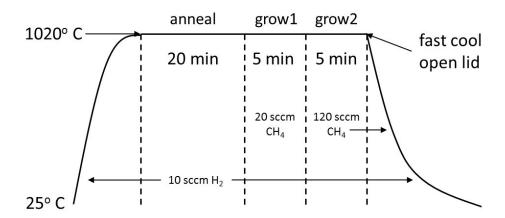

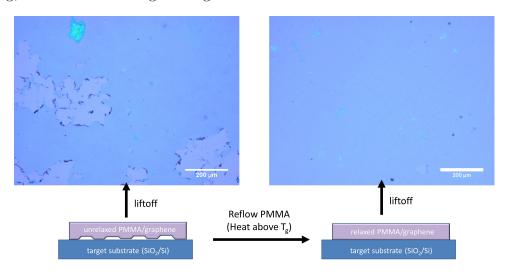

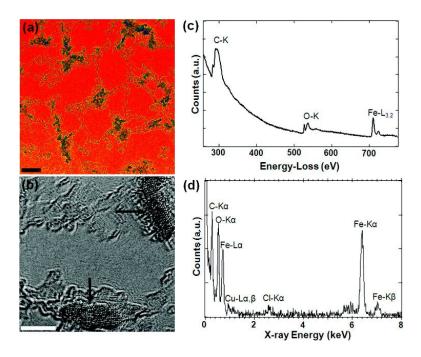

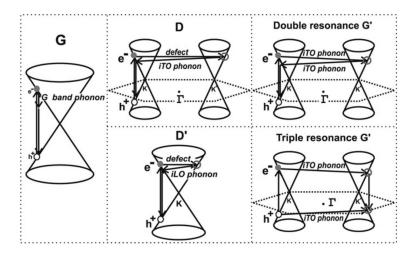

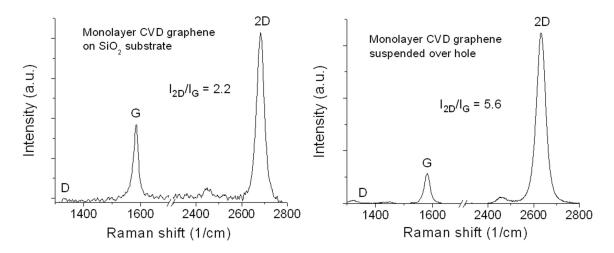

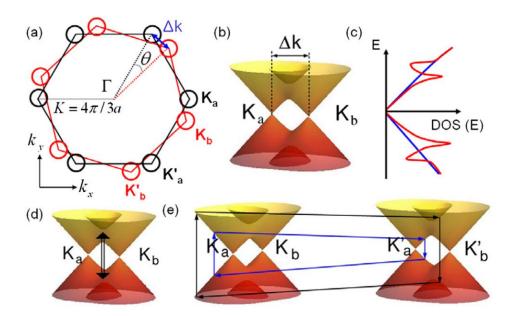

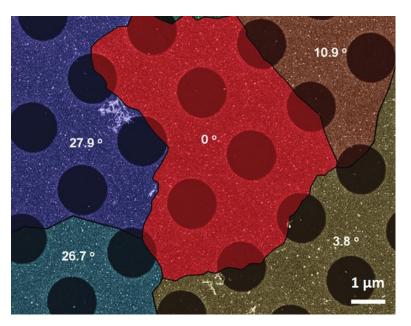

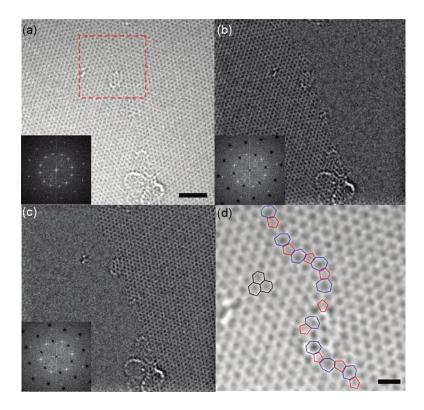

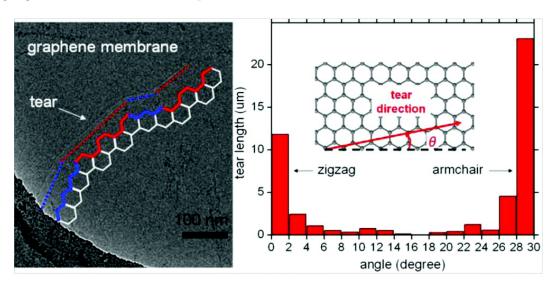

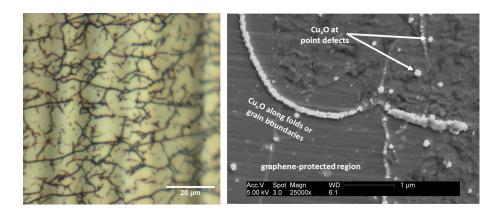

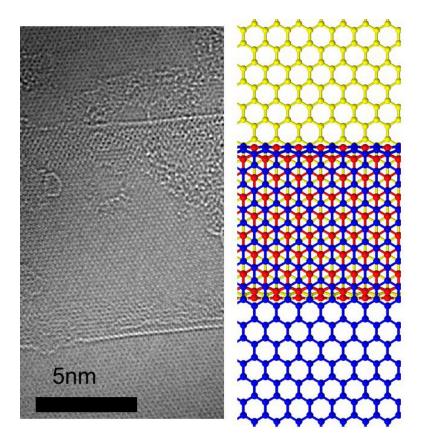

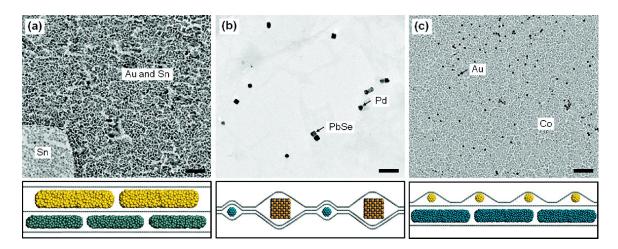

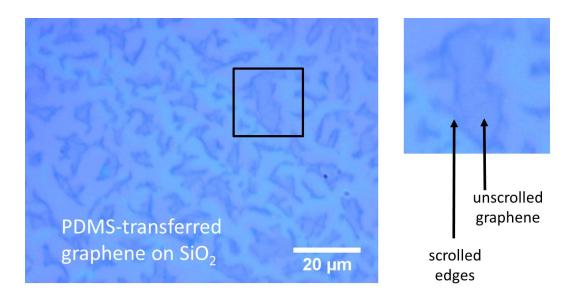

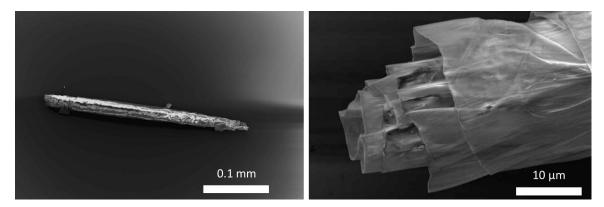

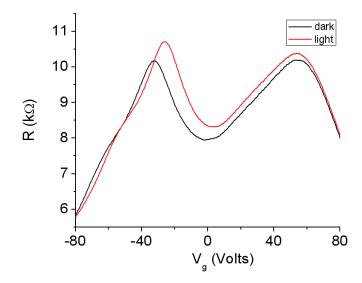

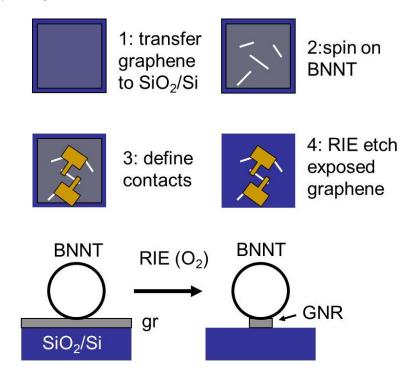

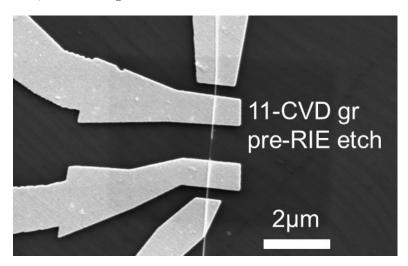

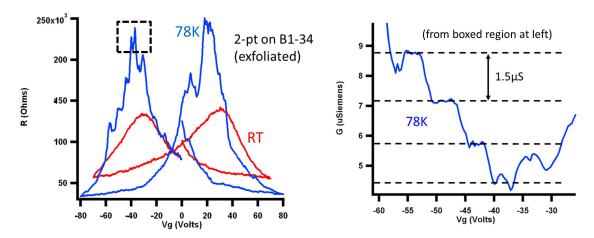

To improve the grain size and quality of graphene, this simple recipe was later modified to a two stage growth process, adapted from Li et al. [64]. This modified recipe, is shown in figure 3.4. As shown in the figure, the two stage recipe begins with a high temperature anneal in H<sub>2</sub>, to reduce the Cu and partially smooth its surface. Next, a low methane pressure growth step yields sparse nucleation of graphene grains, which grow until they begin to touch. To fully stitch together the grains, a higher methane partial pressure is then used. The sample is cooled to room temperature while maintaining H<sub>2</sub> and CH<sub>4</sub> flow. This two-stage CVD graphene has significantly larger grains, typically tens of µm, than the single stage CVD graphene. Additionally,